Copyright is owned by the Author of the thesis. Permission is given for a copy to be downloaded by an individual for the purpose of research and private study only. The thesis may not be reproduced elsewhere without the permission of the Author.

# SCHOOL OF ENGINEERING AND ADVANCED TECHNOLOGY

# Improved Control System for Dual Input-Dual Output DC-DC Converter

Rong CONG

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Engineering

March 2017

### **Abstract**

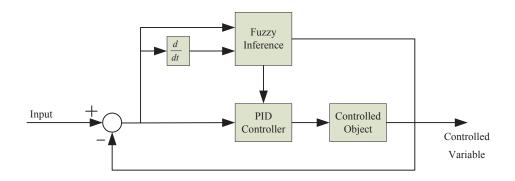

This thesis aims to propose a new control system of dual input dual output DC-DC converter by proposing the advanced fuzzy PID control system. The fuzzy PID controller is a type of intelligent control system being practically applying fuzzy logic theory. Compared with conventional control system, a properly designed fuzzy PID control system is more accurate, sensitive to input, robust to noise, large bandwidth, faster speed and constant oscillation. Therefore, the analysis of improved control system for dual input dual output DC-DC converter, comparison with conventional PID controller, and evaluation are the main focus of this thesis.

The improved control system for dual input dual output DC-DC converter is based on the PID control method and fuzzy logic theory. By the combination of conventional PID controller and fuzzy control theory, the advanced controller with human intelligence is produced. Fuzzy PID control method uses the present error E and EC, combined with the dynamic characteristics of controlled object and practical experience. According to the requirements and target functions, three parameters of PID controller are tuned online by fuzzy rules inference.

Simulation using MATLAB and SIMULINK and implementation with STM32f407 are presented. The optimization of improved control system for dual input dual output DC-DC converter is also studied.

# Acknowledgment

There are many people whom I am very thankful to during my Master study in the past one year. They have significantly helped me in numerous ways that have enabled this thesis to be presented.

First and foremost, I wish to sincerely thank my supervisor, Associate Professor Ibrahim Al-Bahadly, for giving me the most valuable guidance throughout the course of my study. His deep insights and enthusiasm for research in Advanced Controllers on DC-DC Converter has been truly helpful and encouraging. In addition, his limitless source of wisdom and idea has helped me immensely for completing the degree on time.

Secondly, special thanks should go to my colleague, Zubair REHMAN for his help in numerous occasions, particularly for the hardware testing and theoretical analysis. The academic discussions I had with him have made my study very productive and interesting, and his effective suggestions help me find and solve the problems effectively.

Thirdly, I am also very grateful to my friend, Weizhong SHI for his companionship in the journey of my academic career. He encouraged and helped me to go through the toughest time of my project.

Finally, I would like to thank my fiancé, Tong CHE, for his love and caring help. Without his mental support, none of my academic accomplishments would ever been possible. Most importantly, sincere gratitude goes to my mother, Xin LI, for her unconditional love and support, which will be forever remembered deeply in my heart.

# **Contents**

| List of | Figur   | res                                                                | 6      |

|---------|---------|--------------------------------------------------------------------|--------|

| List of | Table   | es                                                                 | 11     |

| Abbrev  | viation | n List                                                             | 12     |

| Chapt   | er 1    | Introduction                                                       | 14     |

| 1.1     | Re      | esearch Background                                                 | 14     |

| 1.2     | Aŗ      | pplication                                                         | 15     |

| 1.3     | Re      | esearch Methodology                                                | 16     |

| 1.4     | Oł      | pjectives of the Thesis                                            | 17     |

| 1.5     | Th      | nesis Organization                                                 | 18     |

| Chapt   | ter 2   | Literature Review                                                  | 20     |

| 2.1     | M       | ulti-input Non-isolated DC-DC Converters                           | 21     |

| 2.      | 1.1     | Dual Input-Single Output DC-DC Converters                          | 21     |

| 2.      | 1.2     | Single Input-Dual Output DC-DC Converters                          | 29     |

| 2.      | 1.3     | Multi Input-Multi Output DC-DC Converters                          | 31     |

| 2.2     | M       | ulti-input Isolated DC-DC Converters                               | 34     |

| 2.3     | Fe      | edback Control System and Proportional-Integral-Derivative Control | lers34 |

| 2.4     | Ac      | lvanced PID Controllers                                            | 39     |

| 2.4     | 4.1     | Increment PID algorithm                                            | 39     |

| 2.4     | 4.2     | Integral-separation PID algorithm                                  | 40     |

| 2.4     | 4.3     | Integral anti-windup PID algorithm                                 | 40     |

| 2.4     | 4.4     | Gradient PID algorithm                                             | 41     |

| 2.4     | 4.5     | Single-input Fuzzy PID algorithm                                   | 41     |

| 2.4     | 4.6     | Fuzzy Logic Control System                                         | 42     |

| _       |         | Theoretical Analysis of Improved Controller on Multi               | _      |

| Convo   | erter   | •                                                                  | 48     |

| 3.1     | На      | ardware Circuit Analysis                                           | 48     |

| 3.2     | Co      | ontrol Method Analysis                                             |        |

| 3.2     | 2.1     | PID Controller                                                     | 58     |

| 3.2     | 2.2     | Fuzzy Logic Analysis                                               | 59     |

| 3.2     | 2.3 Fuzzy PID Control System                             | 61  |

|---------|----------------------------------------------------------|-----|

| 3.3     | Small Signal Modeling                                    | 67  |

| 3.3     | State-space Average Method                               | 67  |

| 3.3     | 3.2 Large-signal Model                                   | 70  |

| 3.3     | 3.3 Linearization and Small Signal AC Equivalent Circuit | 74  |

| 3.3     | 3.4 Transfer Function                                    | 76  |

| 3.3     | The Model of PWM Modulator                               | 79  |

| 3.3     | 3.6 Feedback Controller Design                           | 80  |

| 3.4     | Compensator Design                                       | 82  |

| Chapt   | ter 4 Simulation                                         | 91  |

| 4.1     | MATLAB and SIMULINK                                      | 91  |

| 4.2     | Conventional PID Controller Simulation                   | 91  |

| 4.3     | Fuzzy PID Controller Simulation                          | 104 |

| 4.2     | 2.1 Operation Models Simulation                          | 121 |

| 4.2     | 2.2 Comparison and Analysis                              | 123 |

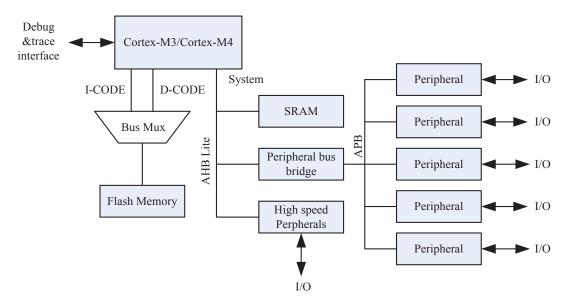

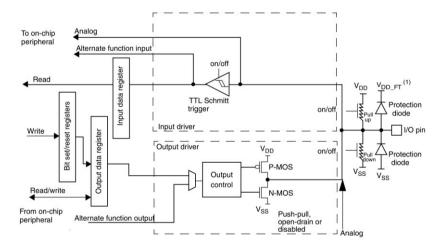

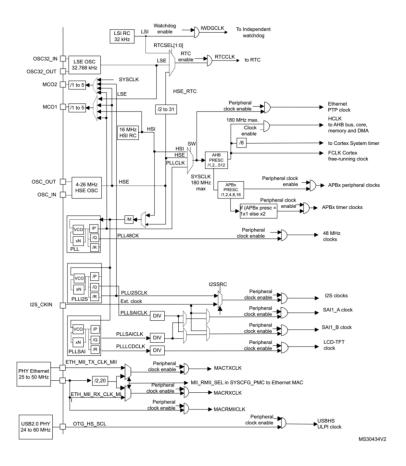

| Chapt   | er 5 Implementation                                      | 126 |

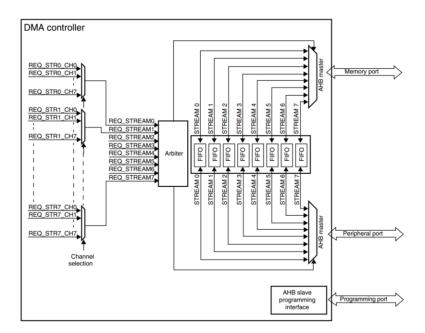

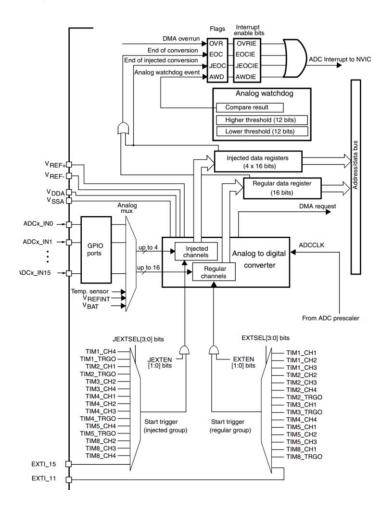

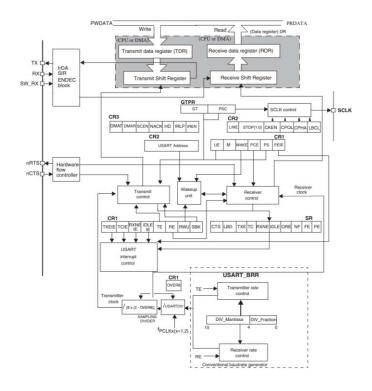

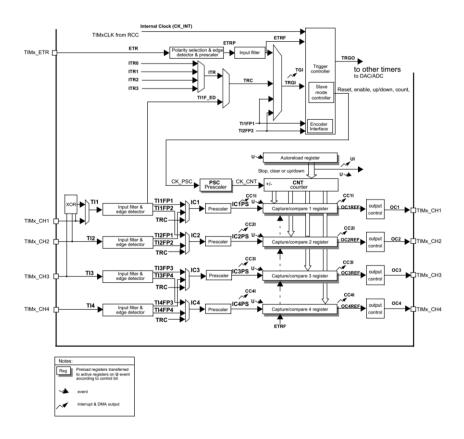

| 5.1     | Introduction of STM32f407                                | 126 |

| 5.2     | Experimental Steps                                       | 137 |

| 5.3     | Experimental Results                                     | 139 |

| Chapt   | ter 6 Evaluation                                         | 146 |

| 6.1     | Results Analysis                                         | 146 |

| 6.2     | Comparison                                               | 149 |

| Chapt   | ter 7 Conclusion and Future Possibilities                | 152 |

| Referen | nce                                                      | 154 |

| Append  | lix                                                      | 161 |

# **List of Figures**

|  | Cha | pter | 1 |

|--|-----|------|---|

|--|-----|------|---|

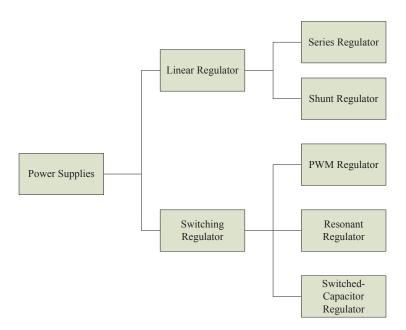

| Fig. 1. 1 Classification of power supplies                                                           | 14      |

|------------------------------------------------------------------------------------------------------|---------|

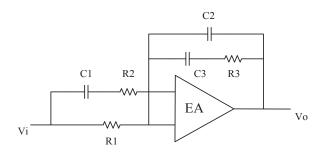

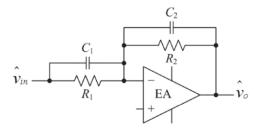

| Fig. 1. 2 Practical implementation of PID compensator with op-amp                                    | 17      |

|                                                                                                      |         |

| Chapter 2                                                                                            |         |

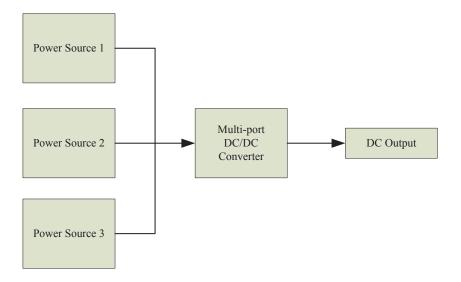

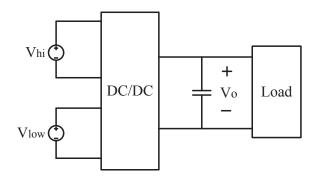

| Fig. 2. 1 Structure of conventional hybrid power system                                              | 20      |

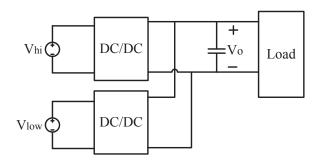

| Fig. 2. 2 Structure of conventional hybrid power system                                              | 22      |

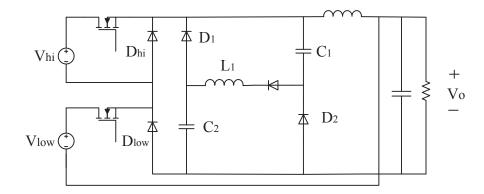

| Fig. 2. 3 Structure of dual-input dc/dc converter                                                    | 22      |

| Fig. 2. 4 Structure of innovative dual-input dc/dc converter                                         | 23      |

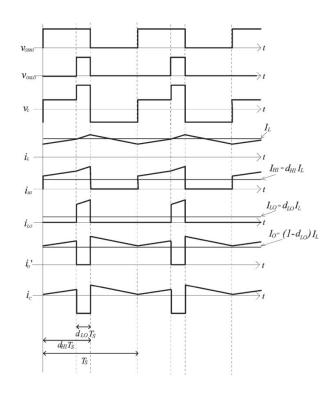

| Fig. 2. 5 Waveform of Proposed dual-input dc/dc converter                                            | 24      |

| Fig. 2. 6 Structure of n-numbered input dc/dc converter                                              | 25      |

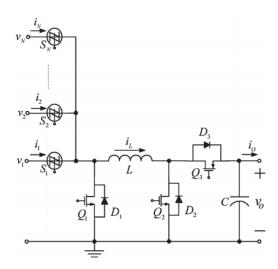

| Fig. 2. 7 Unidirectional multi-input buck-buck converter                                             | 25      |

| Fig. 2. 8 New boost converter structure                                                              | 26      |

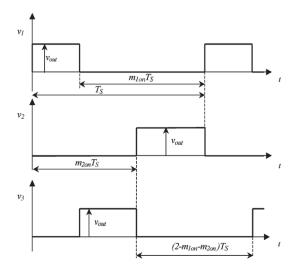

| Fig. 2. 9 Relationship between $v_1$ , $v_2$ , $v_3$ voltages and switch on-duty ratios              | 26      |

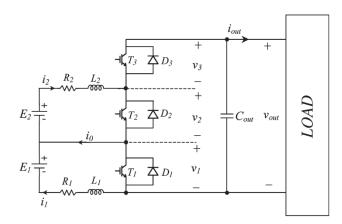

| Fig. 2. 10 Circuit topology of high-efficiency multi-input converter                                 | 27      |

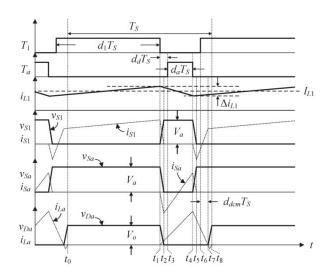

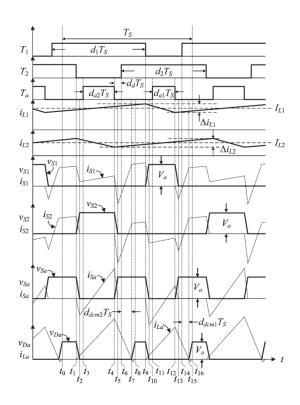

| Fig. 2. 11 Characteristic waveforms in single-power-supply state                                     | 27      |

| Fig. 2. 12 Characteristic waveforms in dual-power-supply state                                       | 28      |

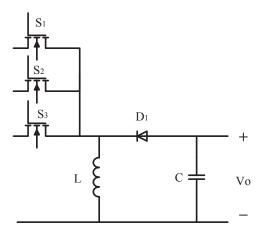

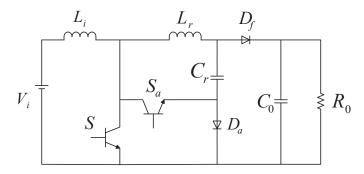

| Fig. 2. 13 The PWM dc-dc boost converter with ZCT cell                                               | 29      |

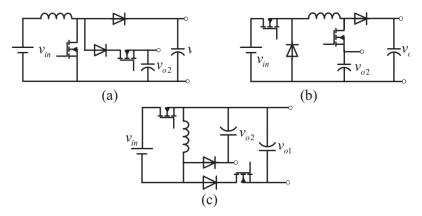

| Fig. 2. 14 Topology of SIDO non-isolated DC-DC converter                                             | 29      |

| Fig. 2. 15 Circuit structure of SIDO converter                                                       | 30      |

| Fig. 2. 16 DC-DC SIDO buck converter                                                                 | 31      |

| Fig. 2. 17 DC-DC SIDO boost converter                                                                | 31      |

| Fig. 2. 18 DC-DC SIDO buck-boost converter                                                           | 31      |

| Fig. 2. 19 The power flow in a three-port converter                                                  | 32      |

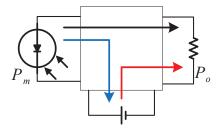

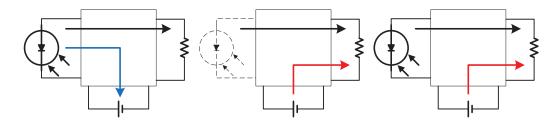

| Fig. 2. 20 Power flow of three-port converters when: (a) $P_m > P_o$ (b) $P_m < P_o$ (c) $P_m = 0$   | 0 32    |

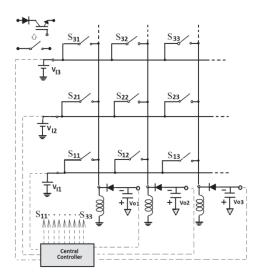

| Fig. 2. 21 Topology of proposed multi-input multi-output buck-boost converter                        | 32      |

| Fig. 2. 22 Topology of proposed multi-input multi-output buck-boost converter                        | 33      |

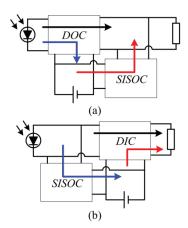

| Fig. 2. 23 Structure of non-isolated three-port converter derived from combination of                | (a) DOC |

| and SISOC, (b) DIC and SISOC                                                                         | 33      |

| Fig. 2. 24 Topology of non-isolated three-port converter                                             | 34      |

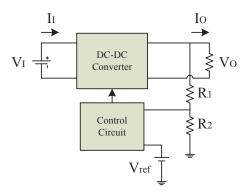

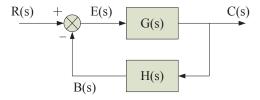

| Fig. 2. 25 Structure of negative feedback control                                                    | 35      |

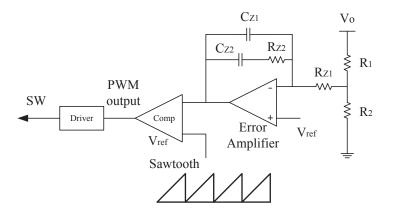

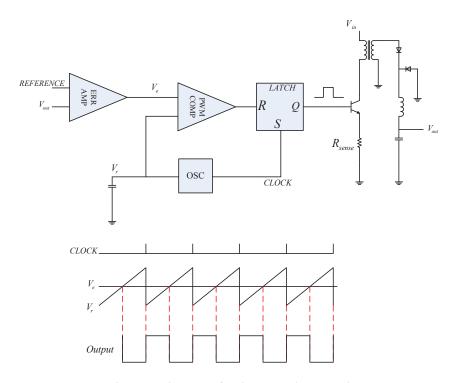

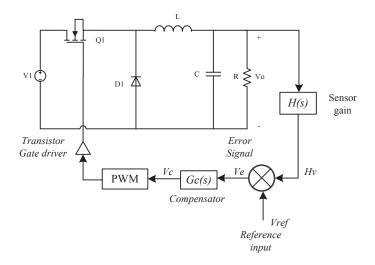

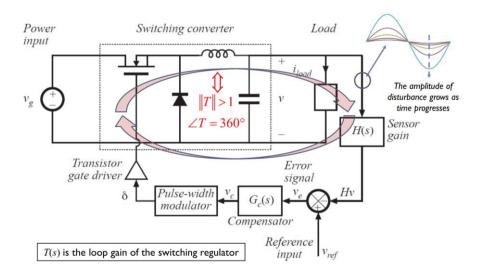

| Fig. 2. 26 Voltage mode regulator for dc-dc converter                                                | 35      |

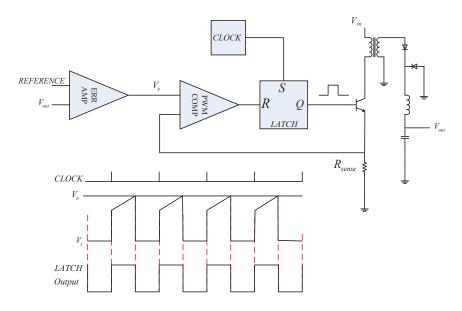

| Fig. 2. 27 Current mode regulator for dc-dc converter                                                | 36      |

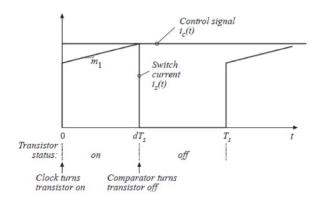

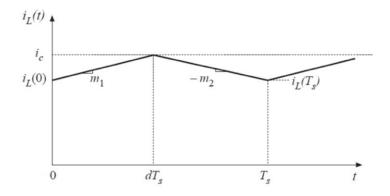

| Fig. 2. 28 Waveform of the inductor                                                                  | 37      |

| Fig. 2. 29 Waveform of a case for $\hat{i}_t(0) > 0$ and $\hat{d} < 0$ with constant $m_1$ and $m_2$ | 37      |

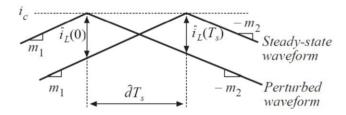

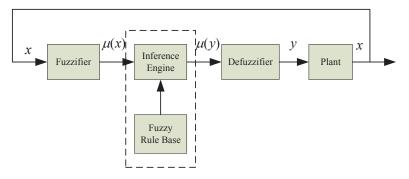

| Fig. 2. 30 Structure of conventional PID controller                                         | 39      |

|---------------------------------------------------------------------------------------------|---------|

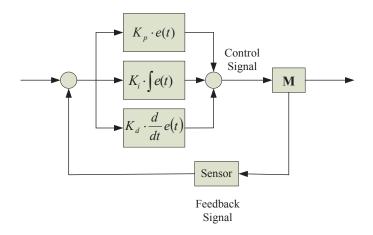

| Fig. 2. 31 Diagram of fuzzy logic control method                                            | 43      |

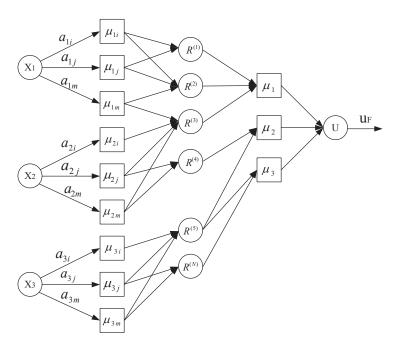

| Fig. 2. 32 The structure of the proposed fuzzy-neural PID controller                        | 45      |

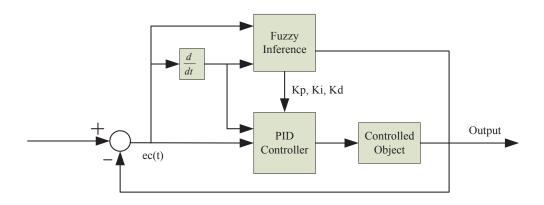

| Fig. 2. 33 The structure of the control system with the proposed fuzzy PID controller       | 46      |

| Fig. 2. 34 The structure of fuzzy self-adaptive PID controller                              | 46      |

|                                                                                             |         |

|                                                                                             |         |

| Chapter 3                                                                                   |         |

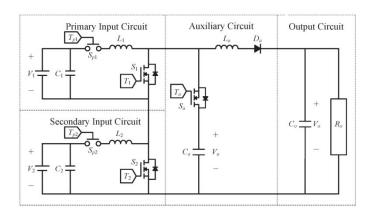

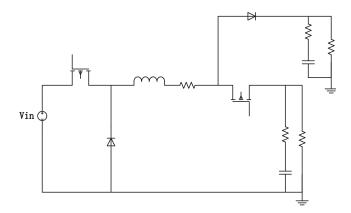

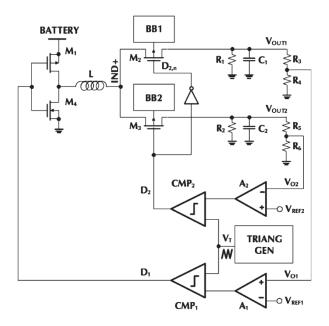

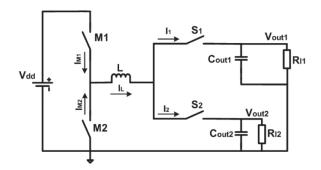

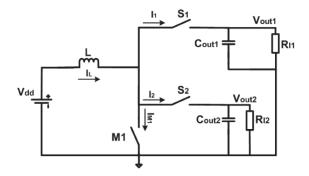

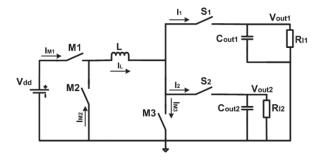

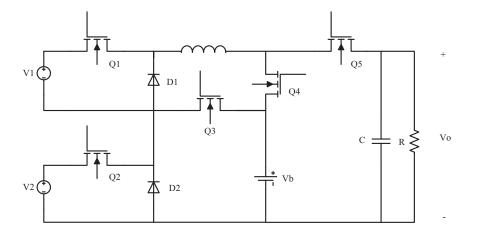

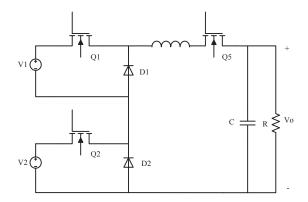

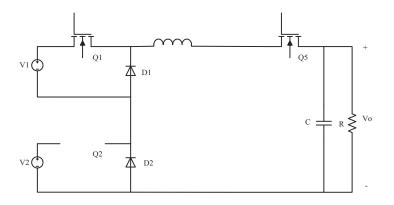

| Fig. 3. 1 Structure of Dual-input Dual-output DC-DC Buck Converter                          | 48      |

| Fig. 3. 2 Structure of Dual-input Dual-output DC-DC Buck Converter                          | 50      |

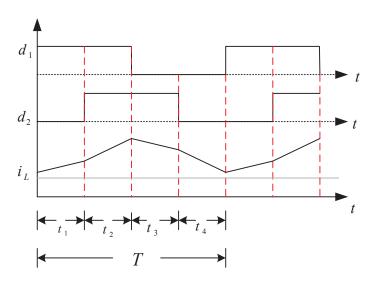

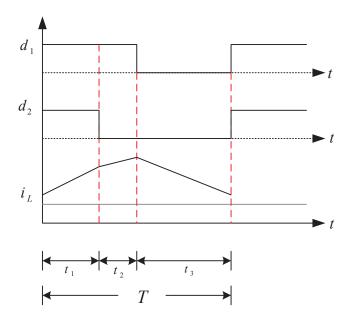

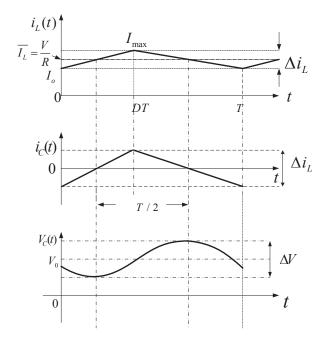

| Fig. 3. 3 Waveforms of dual-input mode                                                      | 51      |

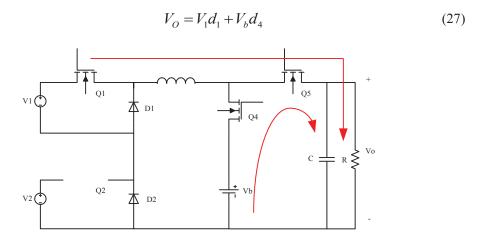

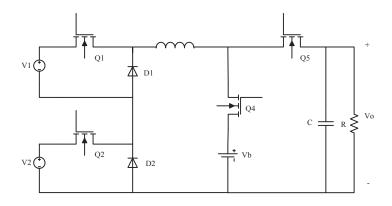

| Fig. 3. 4 Power flow analysis of Dual-input Dual-output DC-DC Buck Converter                | 51      |

| Fig. 3. 5 Equivalent circuit of Dual-input Dual-output DC-DC Buck Converter                 | 52      |

| Fig. 3. 6 Waveforms of dual-output mode                                                     | 53      |

| Fig. 3. 7 Equivalent circuit of SISO converter                                              | 53      |

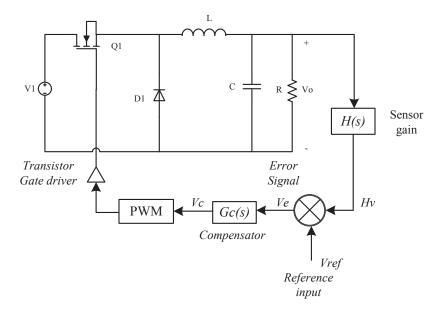

| Fig. 3. 8 Diagram of Voltage Mode Control                                                   | 54      |

| Fig. 3. 9 Diagram of Current Mode Control                                                   | 56      |

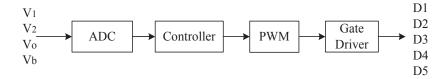

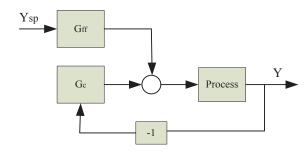

| Fig. 3. 10 Diagram of Control system                                                        | 57      |

| Fig. 3. 11 Basic structure of feedback system for switching regulators                      | 57      |

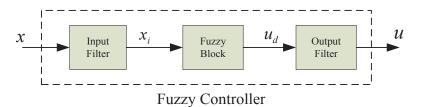

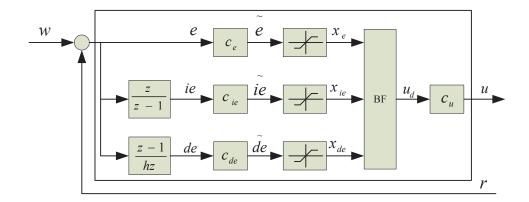

| Fig. 3. 12 The diagram of a fuzzy controller with dynamics                                  | 61      |

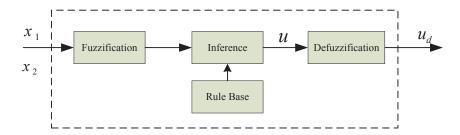

| Fig. 3. 13 The detail structure of a fuzzy block                                            | 62      |

| Fig. 3. 14 The simulation diagram of fuzzy PID controller                                   | 63      |

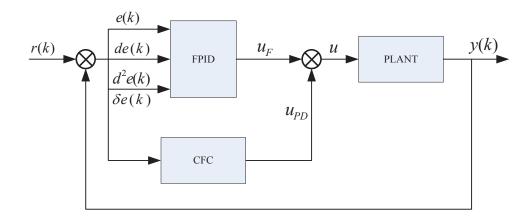

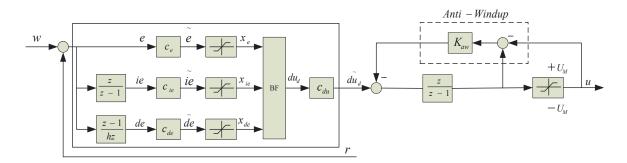

| Fig. 3. 15 The Structure of Anti-wind up Fuzzy PID Controller                               | 66      |

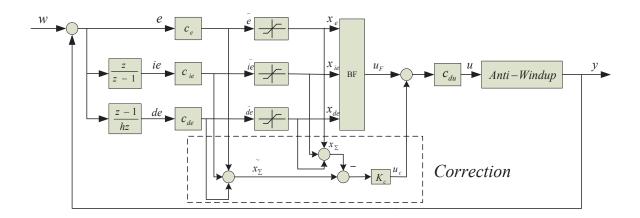

| Fig. 3. 16 The Structure of Anti-wind up Fuzzy PID Controller with Correction Circuit       | 66      |

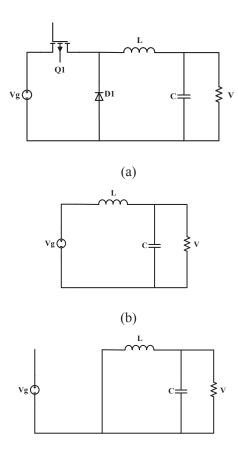

| Fig. 3. 17 Buck converter and its ideal equivalent circuit (a) Circuit (b) Equivalent circu | it when |

| the switch is ON. (c) Equivalent circuit when the switch is OFF.                            | 71      |

| Fig. 3. 18 Idealized current and voltage waveform of buck converter                         | 72      |

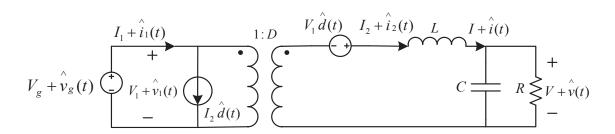

| Fig. 3. 19 Small signal ac equivalent circuit.                                              | 76      |

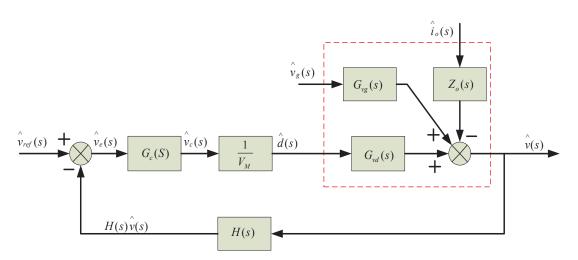

| Fig. 3. 20 Buck DC/DC converter feedback control system                                     | 77      |

| Fig. 3. 21 Linearized Buck DC/DC converter feedback control system diagram                  | 77      |

| Fig. 3. 22 Close-loop control system diagram                                                | 80      |

| Fig. 3. 23 Condition for instability                                                        | 82      |

| Fig. 3. 24 Phase margin and gain margin for stable system                                   | 83      |

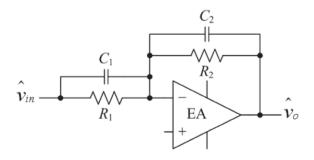

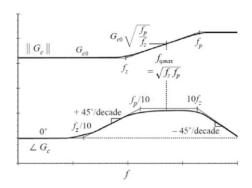

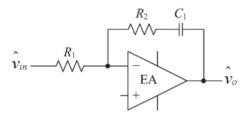

| Fig. 3. 25 Structure of lead PD compensator                                                 | 85      |

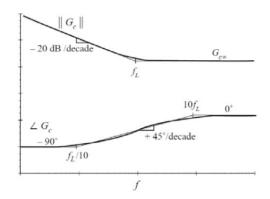

| Fig. 3. 26 Phase margin and gain margin of PD compensator network                           | 85      |

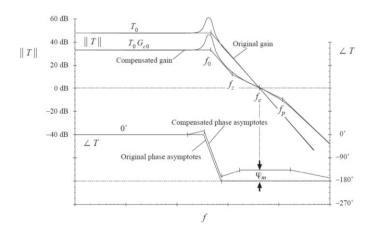

| Fig. 3. 27 T(s) crosses 0 dB at -40 dB/decade                                               | 86      |

| Fig. 3. 28 Structure of lag PI compensator                                                  | 86      |

| Fig. 3. 29 Phase margin and gain margin of PI compensator network                           | 87      |

| Fig. 3. 30 T(s) crosses 0 dB at -40 dB/decade                                               | 87      |

| Fig. 3. 31 Structure of PID compensator                                                     | 88      |

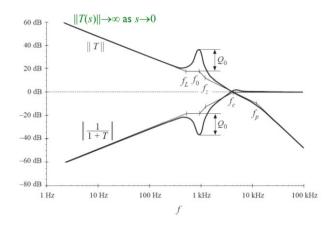

| Fig. 3. 32 Compensated loop gain T(s) with lead-lag PID compensator network                 | 90      |

# Chapter 4

| Fig. 4. 1 Diagram of PID control method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 91         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

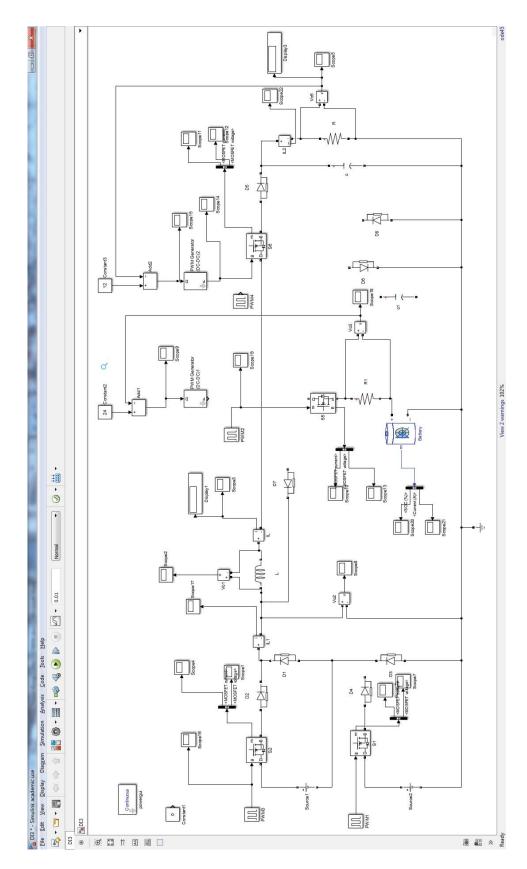

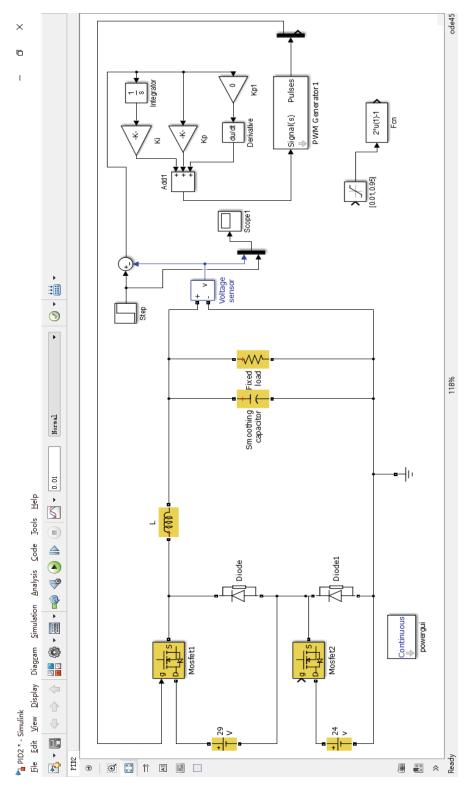

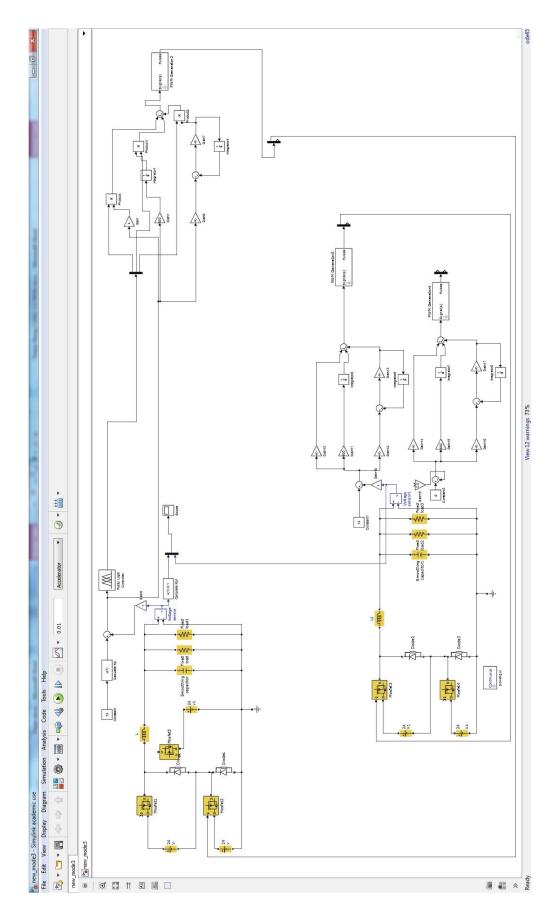

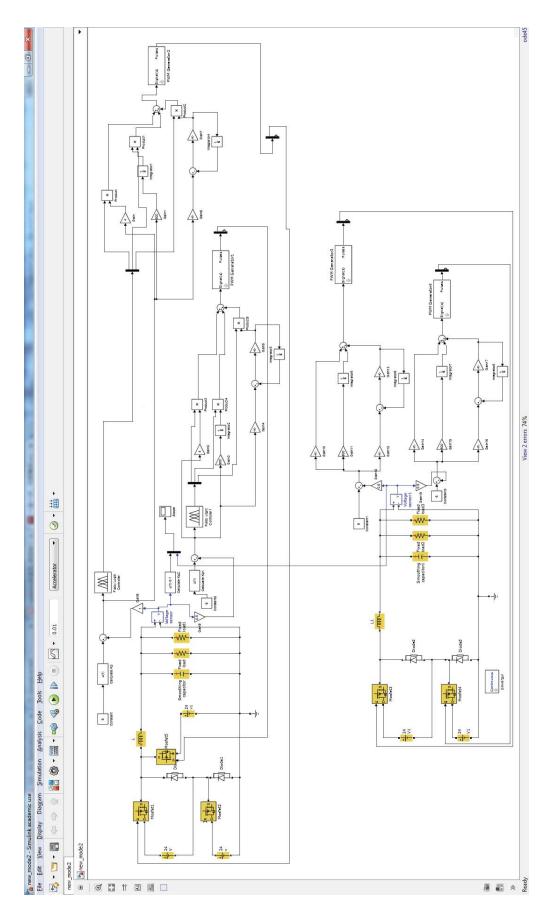

| Fig. 4. 2 Hardware circuit modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 94         |

| Fig. 4. 3 Single-input single-output simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 95         |

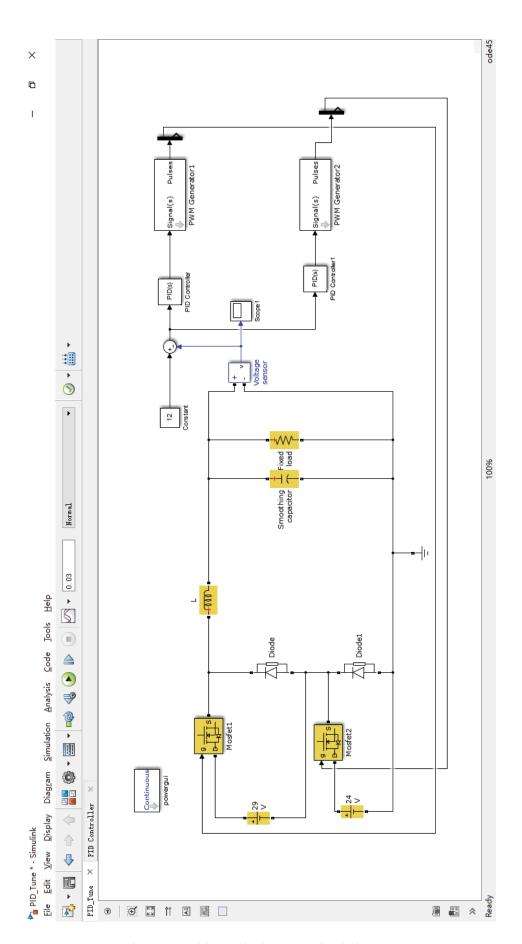

| Fig. 4. 4 Dual-input single output simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 96         |

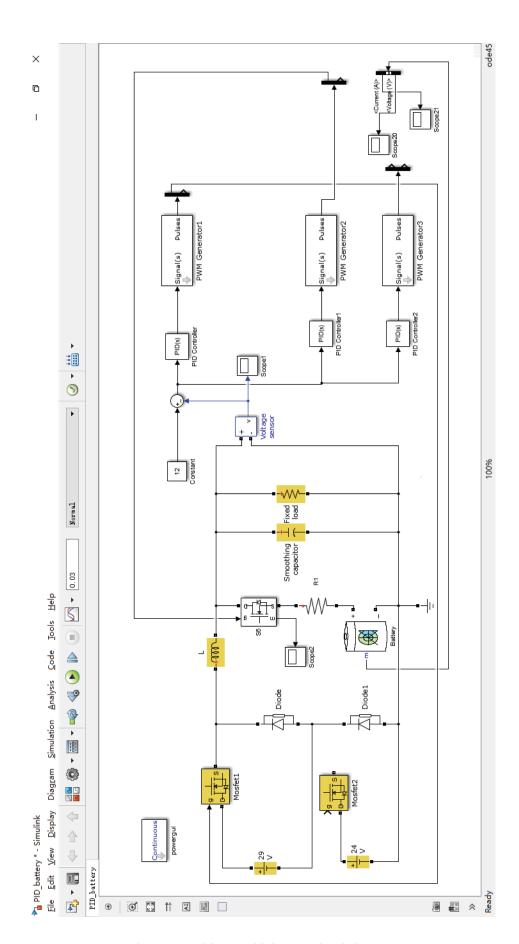

| Fig. 4. 5 Dual-input with battery simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 97         |

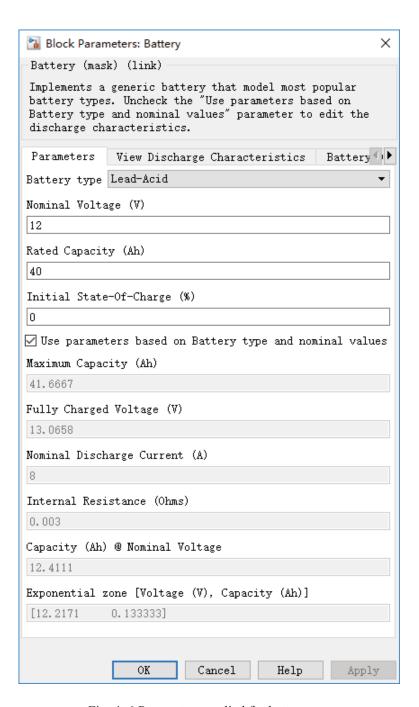

| Fig. 4. 6 Parameters applied for battery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 99         |

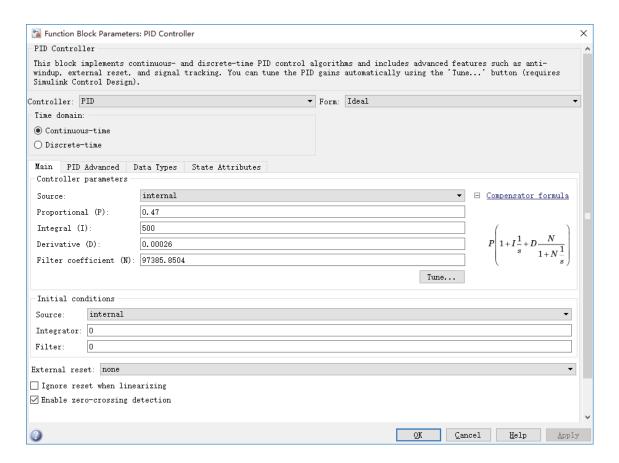

| Fig. 4. 7 Parameters used for conventional PID control simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 100        |

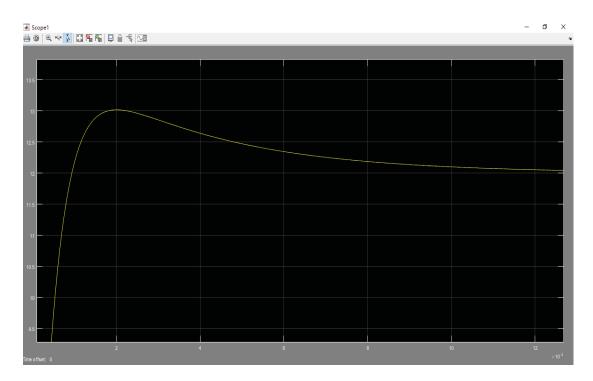

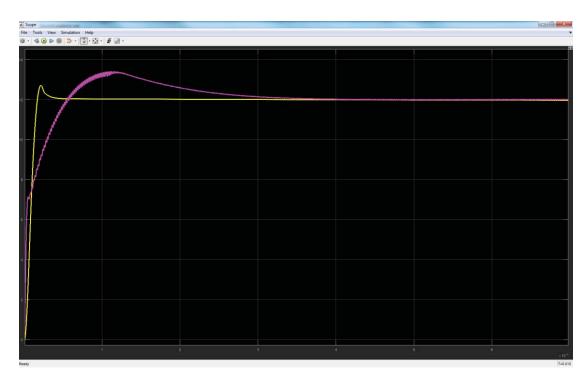

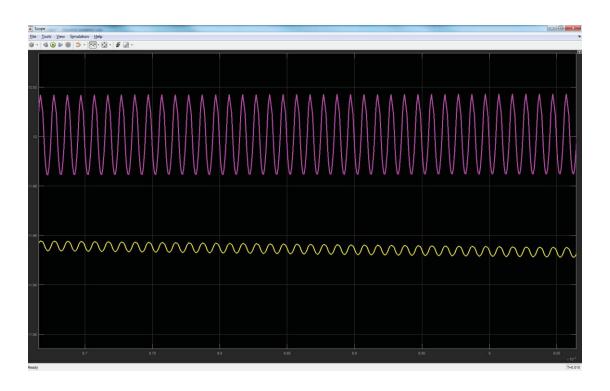

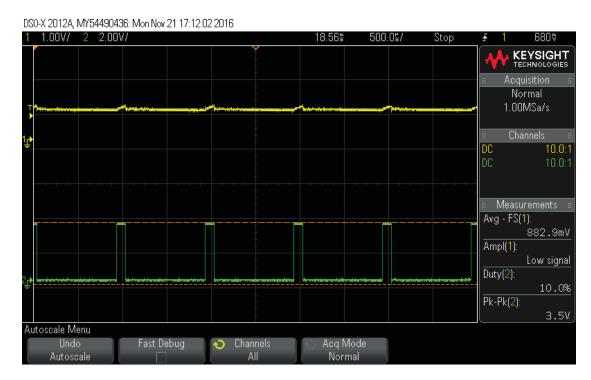

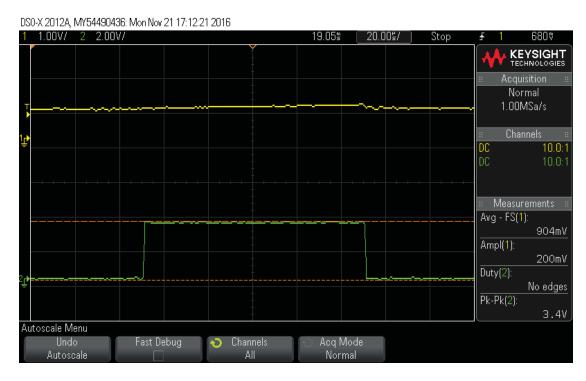

| Fig. 4. 8 Output voltage $v_{out}(0.5 V / div)$ , time scale: $2 ms / div)$ of single-input sing | gle-output |

| mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 101        |

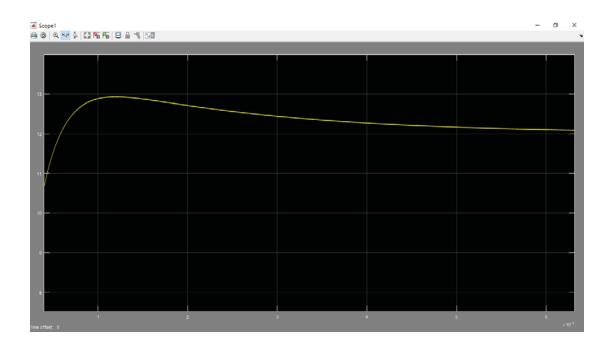

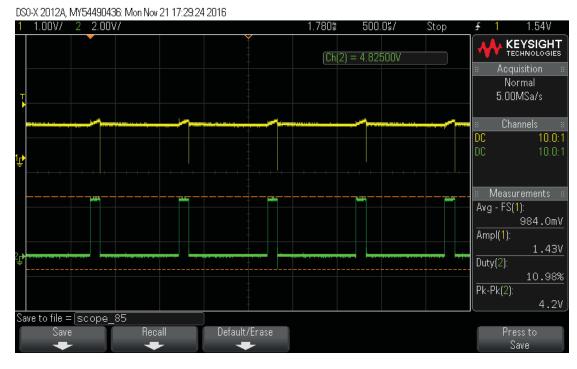

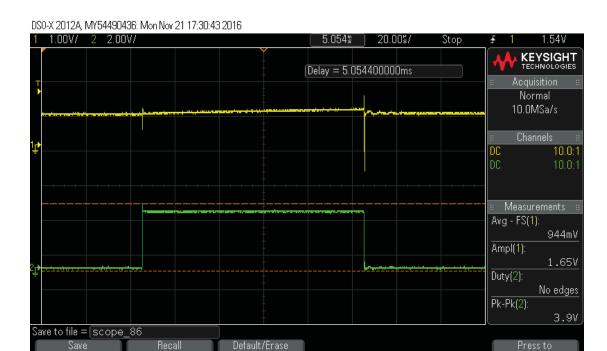

| Fig. 4. 9 Output voltage $v_{out}(0.5 V / div)$ , time scale: $5 ms / div)$ of dual-input sing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | gle-output |

| mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 101        |

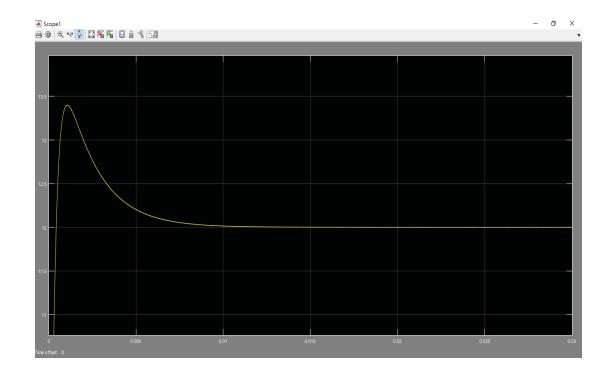

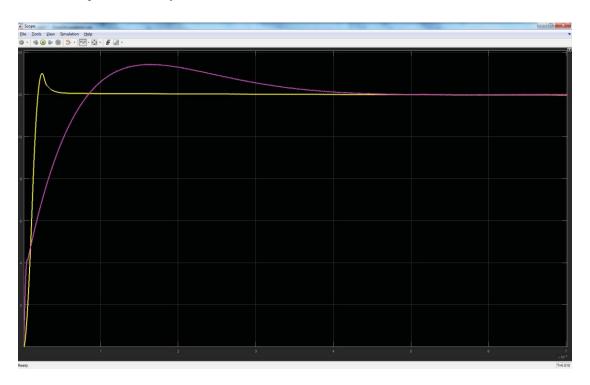

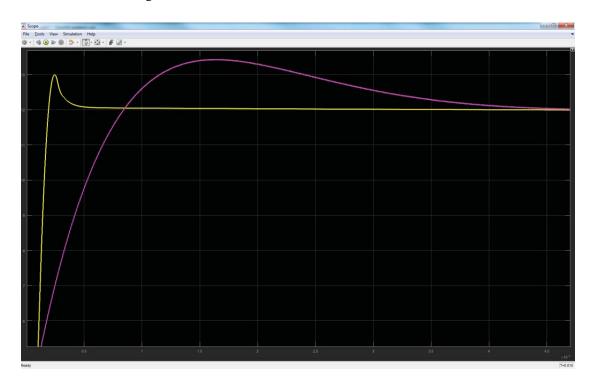

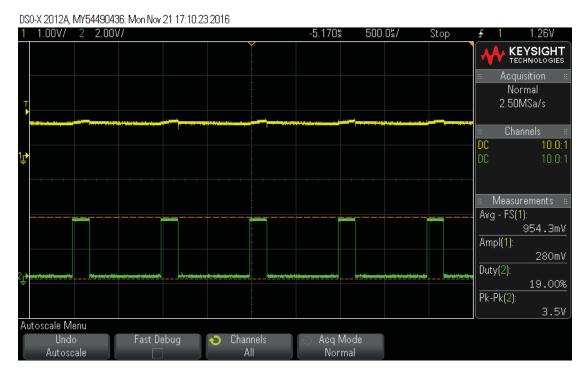

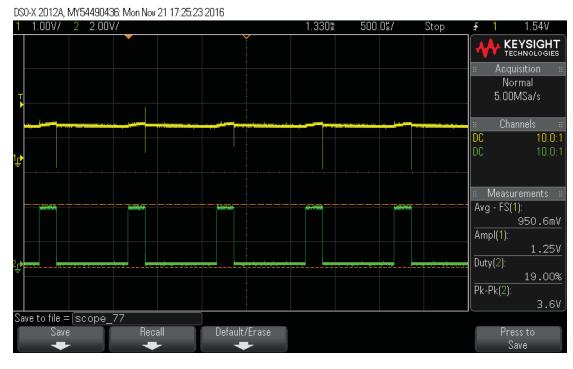

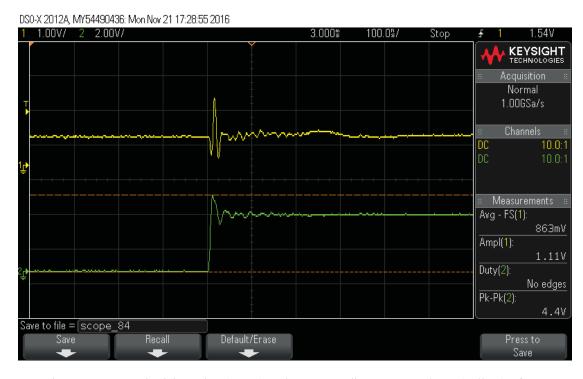

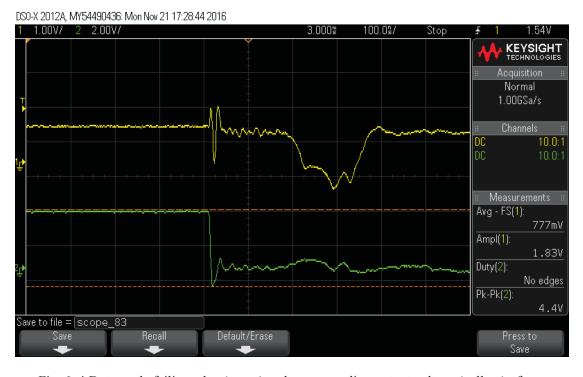

| Fig. 4. 10 Output voltage $v_{out}(0.5 V / div$ , time scale: $1 ms / div$ ) of dual-input defined as $v_{out}(0.5 V / div)$ , time scale: $v_{out}(0.5 V / div)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ıal-output |

| mode with battery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 102        |

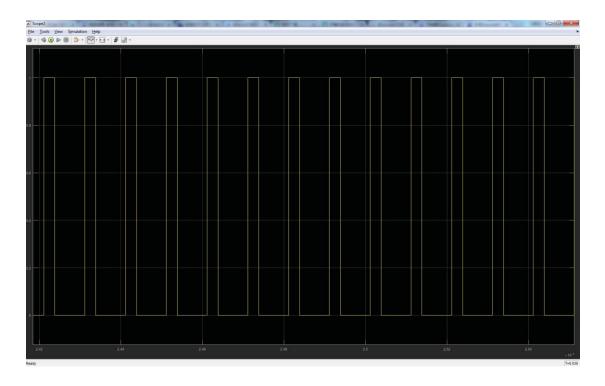

| Fig. 4. 11 Drive signal $v_{gate}$ (0.2 $V$ / $div$ , time scale: 0.1 $\mu s$ / $div$ ) for power switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 102        |

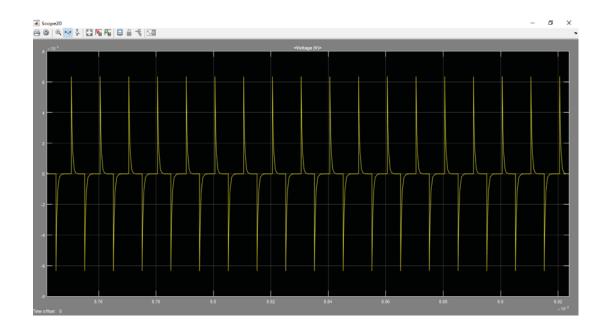

| Fig. 4. 12 Battery voltage $v_{battery}$ (2 $mV$ / $div$ , time scale: 0.1 $\mu s$ / $div$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 103        |

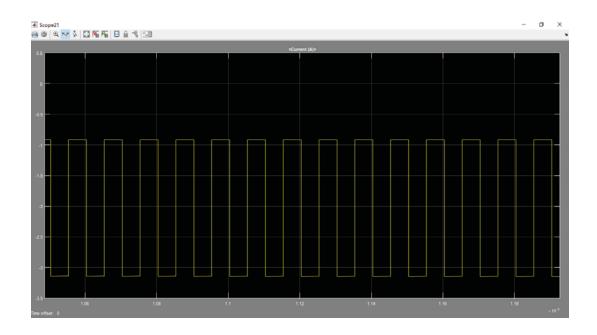

| Fig. 4. 13 Battery current $i_{battery}$ (0.5 $A/div$ , time scale: 0.2 $\mu s/div$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 103        |

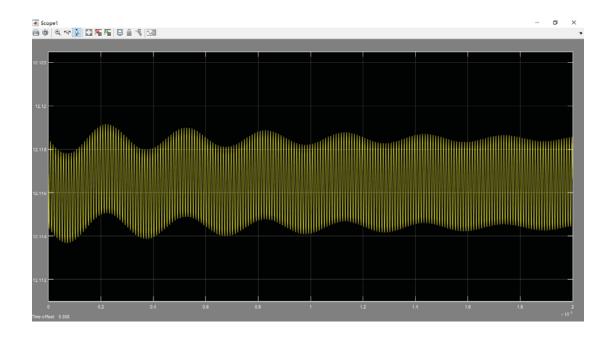

| Fig. 4. 14 Amplified stable output voltage $v_{out}$ (2 mV/div, time scale: $0.2  ms  /  div$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 104        |

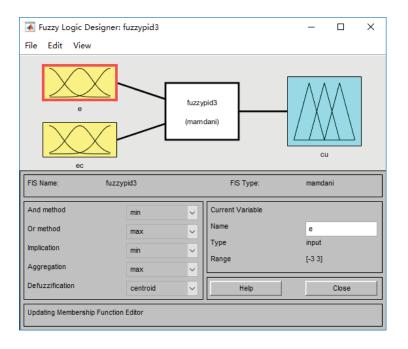

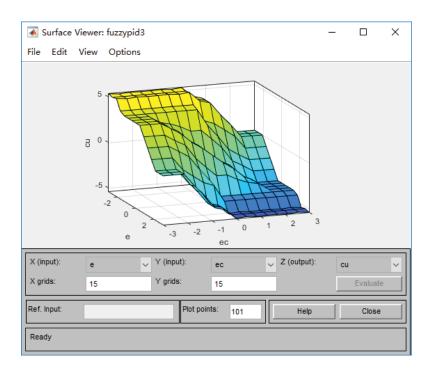

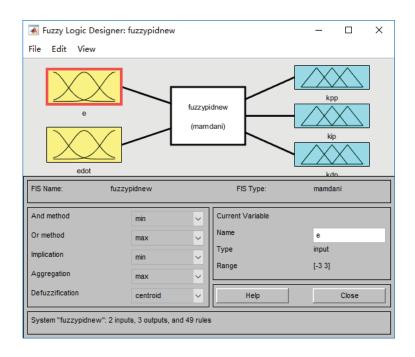

| Fig. 4. 15 Fuzzy PID controller diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 105        |

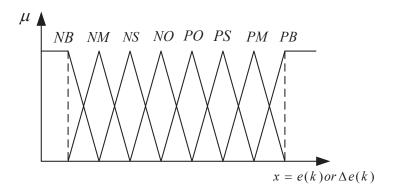

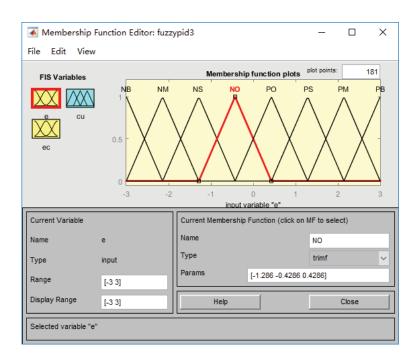

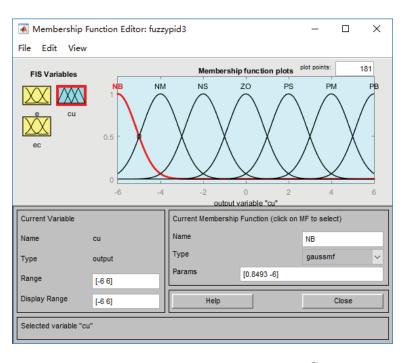

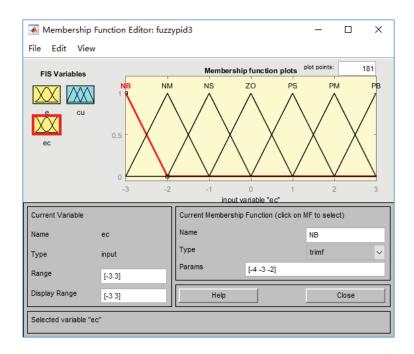

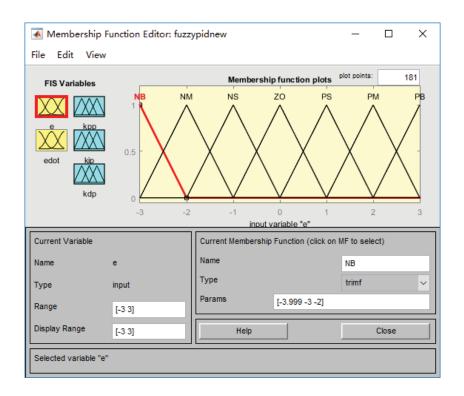

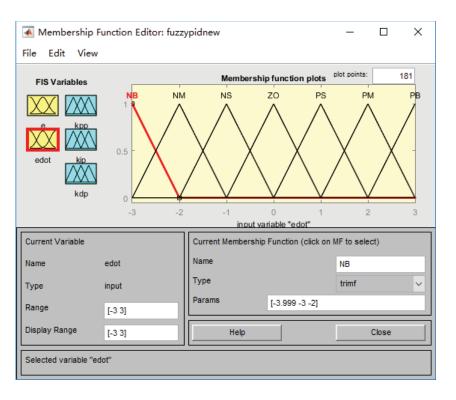

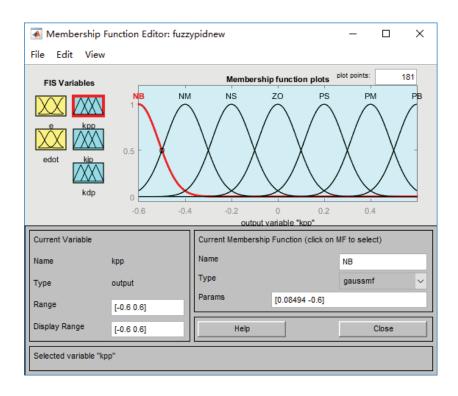

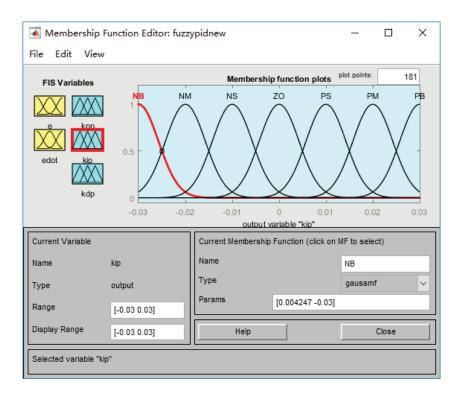

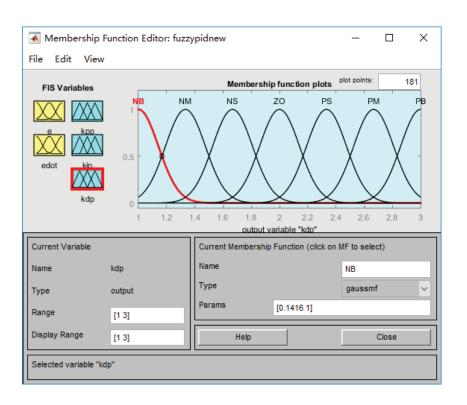

| Fig. 4. 16 Membership function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 106        |

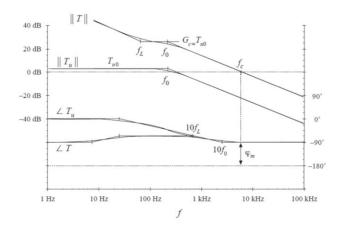

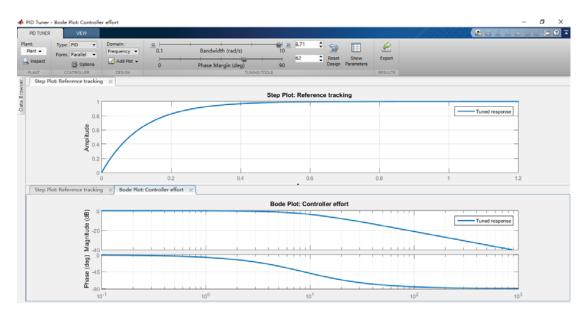

| Fig. 4. 17 The Bode plots of stable control system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 106        |

| Fig. 4. 18 Fuzzy PID controller modeling for single-input mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 108        |

| Fig. 4. 19 Fuzzy PID controller modeling for dual-input mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 109        |

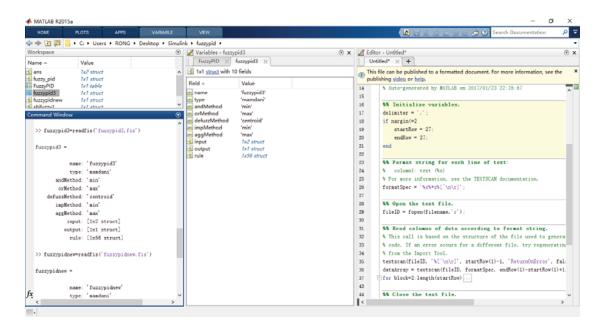

| Fig. 4. 20 Membership function plots for $e(k)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 110        |

| Fig. 4. 21 Membership function plots for $Cu$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |

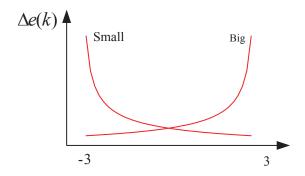

| Fig. 4. 22 Membership function plots for $\Delta e(k)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

| Fig. 4. 23 Membership function editor for the single input mode corresponding relation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nship and  |

| parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |

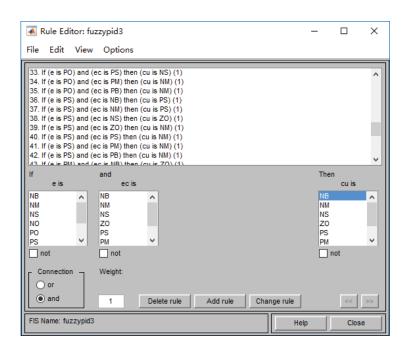

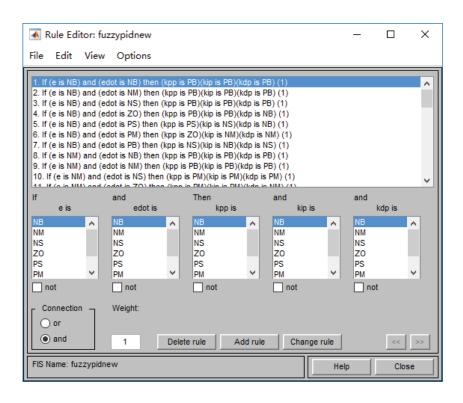

| Fig. 4. 24 Basic rules of fuzzy PID controller for single input mode converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

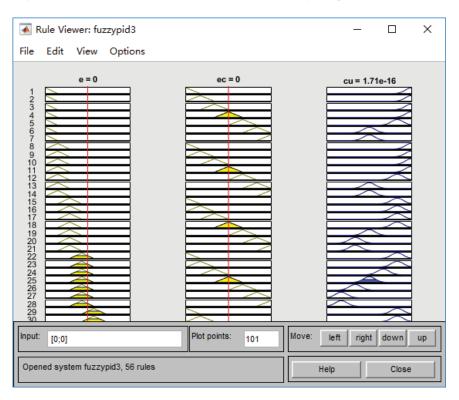

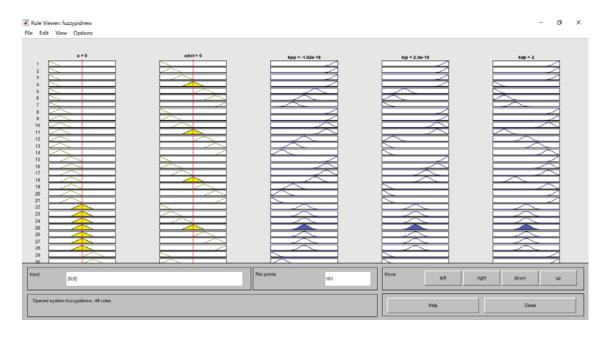

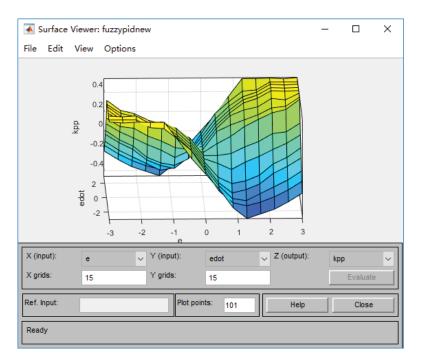

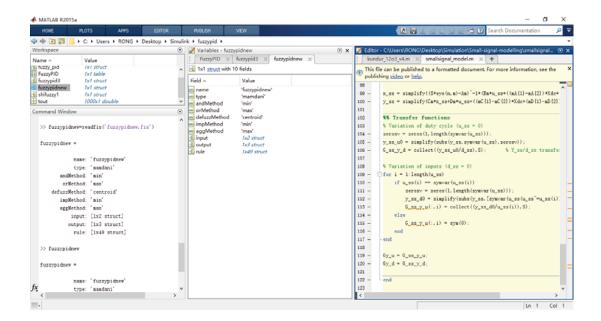

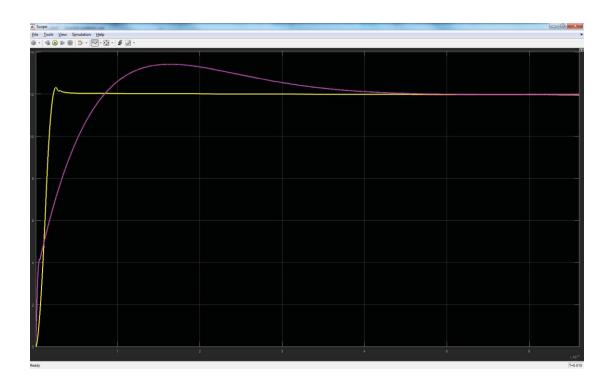

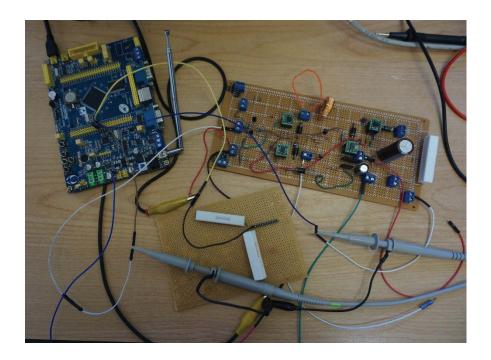

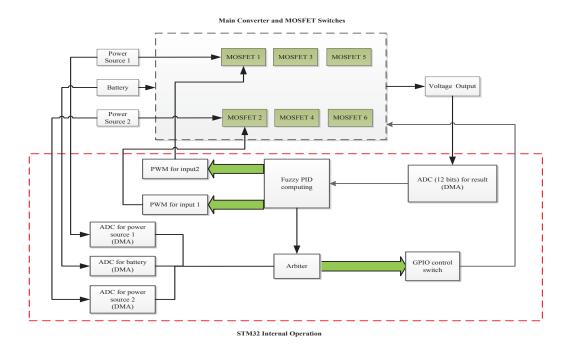

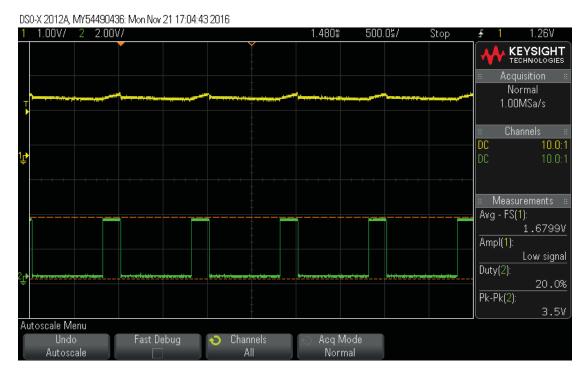

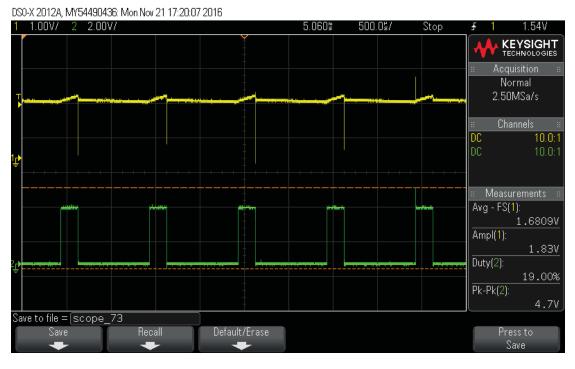

| Fig. 4. 25 Fuzzy rules viewer in MATLAB for single input mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |