## Copyright

Copyright is owned by the Author of the thesis. Permission is given for a copy to be downloaded by an individual for the purpose of research and private study only. The thesis may not be reproduced elsewhere without the Permission of the Author.

# Biomedical Integrated Circuit Design for An Electro-Therapy Device

A Thesis Presented in Partial Fulfilment of The Requirements for The Degree of

### **Doctor of Philosophy**

in

Electronics and Computer Engineering

(Bioelectronics)

at

School of Engineering and Advanced Technology Massey University, Albany Campus, New Zealand

by

### **Ibtisam Abbas**

Full name

(Ibtisam A. Abbas Al-Darkazly)

October 2017

## In the name of God Most Gracious, Most Merciful

#### Dedication

To my parents, whose boundless love and belief in me, from the core of my being, empowered me to be the woman that I am.

To my lovely children and to my talented kids, Zain, Taim and Yoseph, whom are the light in my life.

"Our Actions Today are The Future of The Human Being."

#### **Abstract**

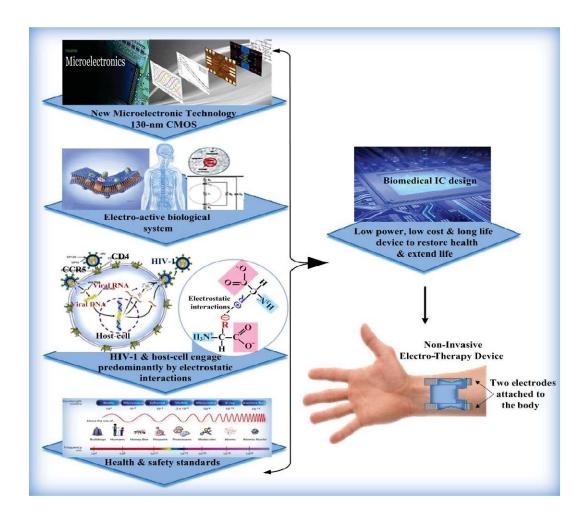

A biomedical integrated circuit design (IC) is utilized for the development of a novel non-invasive electro-therapy device, for low frequency multi-channel biomedical stimulation to transform immune activity and induce anti-viral state. Biomedical integrated circuit design is an important branch of modern electronic engineering that uses the application of electronic engineering principles for biomedical disciplines, to develop bioelectronics devices that are implanted within the body and for non-invasive devices to improve patient's lives. These devices use the application of an electric field to stimulate reactions to restore normal cell functions and activate the cells to treat a variety of disorders or disease conditions. Bioelectronics devices can be designed for use as alternative treatments to overcome the deficiencies of several conventional medical treatments. It could potentially assist as drug-free relief when therapeutic drugs become ineffective, costly, with serious side effects and cannot be replaced, loss of future treatment options, and hence, life threatening, as for drug resistant Human immunodeficiency virus (HIV-1) patients.

Since the underlying mechanisms of the biological system and disease state is dominated by electrostatic interactions, specifically, the interaction between HIV-1 and the host cell that is predominantly by electrostatic interactions (protein charge-charge interaction) has an important role in its life cycle replication. At given pulses, the charge distribution and polarization of the electro-active protein molecules takes place, inducing conformation change which can enhance immune activity and inhibit the interaction of HIV-1 and host cells, disturbing its life cycle, leading to the mechanisms of the inactivation signal-induced virus death. These electrically induced protein transformations is used in this research as blood-cell treatment and as anti-HIV-1 electrotherapy.

Advances in bioelectronics technology, which involve new CMOS IC design, and in bio-electrochemistry science, which include cellular function, electro-active biomolecules and their responses, have contributed to this project to develop the concept of a novel electro-therapy device, for biomedical treatment applications. This involves understanding of the underlying mechanisms of the biological system and disease condition from an electronic engineer's point of view as well as the interface

between the electronic signal and the biological cells, and how electronic devices and circuitry directly communicate with the electro-active body tissue and blood cells.

This research project addresses the design and development of a novel energy-efficient miniature biomedical device using a new CMOS technology. It can generate, deliver and control an appropriate periodical low frequency electrical pulses, through the low-resistance skin surface to a patient's blood. The notable feature of such a smart device is its cellular specificity: the parameters of the generated electrical pulse which are designed and selected in order to stimulate only one particular type of tissue (blood) leaving the others unaffected. The device comprises a mixed-signal low power dual-band waveform generator (WFG) chip along with a novel two band tuning system. It was fabricated using Global Foundries (GF) 8RF-DM 130-nm CMOS process with a supply voltage of ±1V for the analog circuit and +1V for logic circuits. The WFG core (band I) can be tuned in the range 6.44 kHz - 1003 kHz through bias current adjustment, while a lower frequency (band II) in the range 0.1 Hz to 502 kHz can be provided digitally. Two WFG approaches, that comprise relaxation oscillators with different relaxation timing networks, have been developed for comparison.

Since the aim of this work is to transfer electrical signal in a specifically controlled fashion through the tissue, a novel low power active electrode-pair signal delivery system, compatible with human skin with high signal integrity, is developed. The circuit was fabricated in a 130-nm CMOS process using a low supply-voltage of +1.2V to deliver bi-phase square waveform signals from 16 selectable low-frequency channels. The individual active electrode can also be used to deliver mono-phase square/triangular waveform output signals. Accuracy, safety, low power, light-weight, miniature and low-cost characteristics are the main concerns. Being a miniature bioelectronics component with low power consumption, the proposed device is suitable both as a non-invasive and as an implantable biomedical device, in which WFG and electrodes circuitry can communicate with the electro-active biomolecule, strongly stimulating certain events in a complex biological system.

A theoretical analysis, experiment design and performance are carried out in invitro environments to examine the effect of the designed signal on human blood cellular proteins. Proteins that display a heterogeneous structure have various conductivities and permittivity (determining the interaction with the electrical field) and possess dielectric properties with a large conformation change, undergoing structural rearrangements in

response to cellular signals. The frequency-dependent dielectric present in proteins involves the redistribution and alignment of the proteins charged molecule and its polar molecule in response to an applied external electrical field can also induce conformation change. Interference polarization within proteins could interrupt the interaction between both sides of predominantly host cell proteins and of the HIV-1 infective envelope and its protein particles. This could disturb the signalling proteins for cell activation, and, hence, the virus cannot conjugate with the target cells and control the host cell protein activity. Since the virus is unable to reproduce out of a host cell, hence the virus cannot mutate and develop resistance easily, and use alternative binding and entry mechanisms as in the pharmacological approaches. After carefully studying the interaction of the HIV-1 virus and the host cell, with respect to signal transfer, CD4 receptor, co-receptors CCR5 and nuclear transport factor nucleoporins FGNup153 proteins of the lymphatic system, which are essential targets for HIV-1 infection and its life cycle replication represent an attractive target to investigate in this research project. The activities of the target cell are then underlying mechanism of the examined utilizing immunofluorescence microscopy technique with specific fluorescent labelled antibodies, and accurate results are obtained with relatively low cost. The results demonstrated that the low frequency electrical pulse could inhibit virus attachment and fusion. It is also could provide a permeability barrier, that prevents the import and export of large macromolecule virus particles through the nuclear pore complex. These effects could induce an antiviral state for a period of time, and stope HIV-1 virus replication, with no potential risks and harm to the host cells, compared to the common drugs. This is promising for the conception of HIV-1 treatment in vivo. Although further investigations are required in order to fully use the application of electrical stimulation in vivo for treatment, the result is provides the necessary impetus for the applications of low frequency electrical stimulation on human immune response. This might offer important antiviral therapy against the most devastating pathogens in human history.

This doctoral research is not only of academic interest but also highly relevant to medical applications. It is considered potentially beneficial in the development of knowledge in advanced technology for electro-medical treatment devices, their design, structure and applications to extend life, and for future growth in the biotechnology industry, therefore beneficial for the patients, physicians and for humanity.

### Acknowledgments

The compilation of this research project would not have been possible without the support of others which is sincerely appreciated and thankfully acknowledged. Foremost, I would like to acknowledge and thank my supervisor Dr. Rezaul Hasan, for his valuable guidance, kindly encouragement and scholarly advice at various stages throughout my study. I would like to thank my supervisor Dr. Rezaul Hasan once again for facilitating the funding of this work through Massey University.

I would like to acknowledge the Massey University for financial support for the funding of this work. I also would like to acknowledge the Massey University Human Ethics Committee, Dr. Brian Finch, Human Ethics Chairs' Committee and Director, Mr. Jeremy Hubbard, Human Ethics Chairs' Committee: Southern A and to Ms. Patsy Broad, team leader. I would like to mention the facilities in the laboratory of Human Nutrition, School of Food and Nutrition (SoFN) laboratories, College of Health at Albany campus, Massey University for in-vitro biological tests as part of this work.

I am grateful to Dr. Pamela Von Hurst co-director of vitamin D research center for her keen interest in supporting the researcher and her prompt kind encouragement regarding lab facilities and safety. I would further like to thank Dr. Cath Conlon for providing me with a place in the Human Nutrition lab. I thank Mr. James Connell compliance support officer and Mr. PC Tong and Mrs. Rachel Liu for the use of lab facilities and for the health and safety induction in lab building 27 and lab building 10. I also thank profusely Dr. Peter Flanagan, National Medical Director, New Zealand Blood Service for providing a Blood sample. I also would like to acknowledge chip fabrication support from MOSIS.

I would like to thank the staff at School of Engineering and Advanced Technology for their support during my study. I thank Mr. Joe Wang for electronic lab facilities and Mr. Roukin Dmitri for the use of Linux programme. I also would like to thank my friends and colleagues for all of the valuable words of encouragement. I would further like to thank my thesis proof reader, Mrs. Diana Hibbert.

Finally, I would like to thank my family. Their love, sacrifice, patience and encouragement cannot be replaced by anything else in this world. I'm forever grateful to them.

## **Table of Contents**

| Abstract                                                               | iii   |

|------------------------------------------------------------------------|-------|

| Acknowledgements                                                       | vi    |

| Table of Contents                                                      | vii   |

| List of Abbreviations                                                  | xii   |

| List of Symbols                                                        | xiv   |

| List of Figures                                                        | XV    |

| List of Tables                                                         | xxiii |

| Chapter 1. Introduction                                                | 1     |

| 1.1 Biomedical Integrated Circuit Design                               | 1     |

| 1.2 Relevance                                                          | 6     |

| 1.2.1 Virus Replication                                                | 7     |

| 1.3 Develop Concept                                                    | 10    |

| 1.4 Research Goals                                                     | 16    |

| 1.5 Scope of This Study                                                | 16    |

| 1.6 Thesis Overview                                                    | 20    |

| Chapter 2. Overview of The System Model, Theory, Design and Approaches | 23    |

| 2.1 Introduction                                                       | 23    |

| 2.2 Waveform Generator Overview                                        | 24    |

| 2.3 Basic Theory of Oscillator                                         | 26    |

| 2.3.1 Oscillators Approaches                                           | 28    |

| 2.3.2 Relaxation Oscillator Architecture                               | 30    |

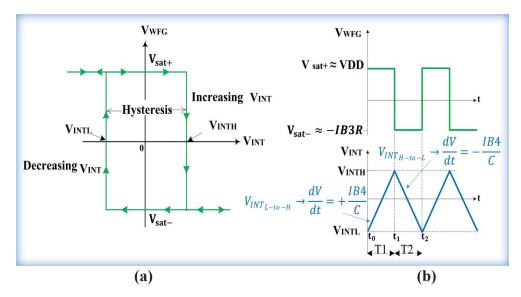

| 2.4 Hysteresis Schmitt Trigger Concept                                 | 30    |

| 2.5 Principles of Operation of Typically WFG Circuit                   | 33    |

| 2.5.1 Theory of WFG Based on RC Network                                | 33    |

| 2.5.2 Theory of WFG Based on Integrator                                | 35    |

| 2.6 Waveform Generator Approaches                                      | 36    |

| 2.6.1 Relaxation Timing Network Approaches                             | 46    |

| 2.6.1.1 Passive RC Approaches                                          | 46    |

| 2.6.1.2 Active Integrator Building Block Approaches                    | 48    |

|           | 2.7     | Tuning Circuit Approaches                                      |

|-----------|---------|----------------------------------------------------------------|

|           | 2.8     | Digital Model for Frequency Divider                            |

|           | 2.8     | .1 Frequency Divider Theory                                    |

|           | 2.8     | 2 Flip Flop Approaches                                         |

|           | 2.8     | 3 Sources of Power Dissipation In A Digital Model              |

|           | 2.9     | Active Electrode                                               |

|           | 2.10    | Conclusion                                                     |

| Chapter 3 | . Desig | gn Criteria, Implementation and Fabrication of Waveform        |

|           | Gene    | erator Circuit for Extra Low-Frequency CMOS Micro-             |

|           | Powe    | er Applications                                                |

|           | 3.1     | Introduction                                                   |

|           | 3.2     | Trade-off of Low Power CMOS WFG Design Analysis                |

|           | 3.3     | Design Criteria of CMOS ELF WFG Circuit                        |

|           | 3.4     | Circuit Design and Topology of The ELF WFG                     |

|           | 3.5     | Circuit Operation of The ELF WFG                               |

|           | 3.6     | Simulation and Performance Analyses of The ELF WFG             |

|           | 3.6     | .1 Amplitude Control of The ELF WFG                            |

|           | 3.6     | 2 Frequency Control of The ELF WFG                             |

|           | 3.7     | Layout and Fabrication of The ELF WFG                          |

|           | 3.8     | Experimental Results of The ELE WFG                            |

|           | 3.9     | Conclusion.                                                    |

| Chapter 4 | . Desig | gn Criteria, Implementation and Fabrication of Dual-Band       |

|           | CMO     | OS Waveform Generator With Ultra-Wide Low-Frequency            |

|           | Tuni    | ng Range                                                       |

|           | 4.1     | Introduction                                                   |

|           | 4.2     | Design Criteria of CMOS Dual-Band WFG <sub>INT</sub>           |

|           | 4.3     | Circuit Design and Topology of The WFG <sub>INT</sub>          |

|           | 4.3     | .1 WFG <sub>INT</sub> Circuit Design                           |

|           | 4.3     | 2 Hysteresis Schmitt Trigger Circuit of The WFG <sub>INT</sub> |

|           | 4.3     | .3 Gm-C Integrator Realization                                 |

| 4.3.4 WFG <sub>INT</sub> Circuit Operation                           | 117 |

|----------------------------------------------------------------------|-----|

| 4.3.5 Components Sizing for Low Power & Low Frequency                |     |

| WFG <sub>INT</sub> Design                                            | 121 |

| 4.4 Frequency Tuning Technique                                       | 125 |

| 4.4.1 Analog Tuning Model                                            | 125 |

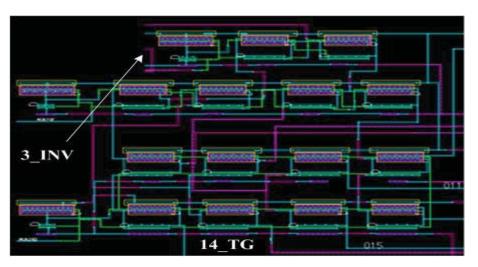

| 4.4.2 Digital Model Implementation                                   | 126 |

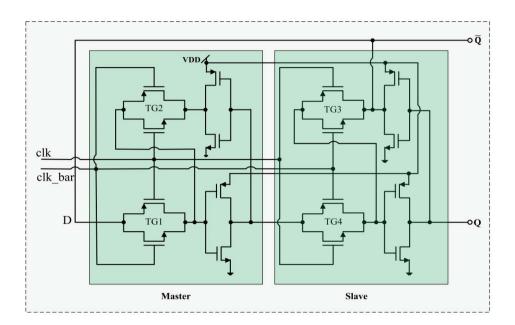

| 4.4.2.1 Clock and Clock_Bar                                          | 126 |

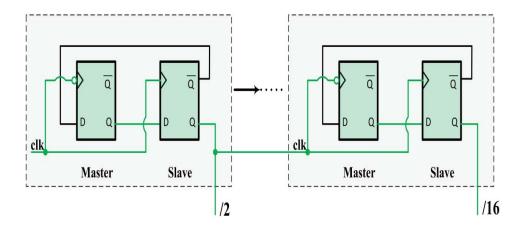

| 4.4.2.2 The Frequency Division Circuit                               | 126 |

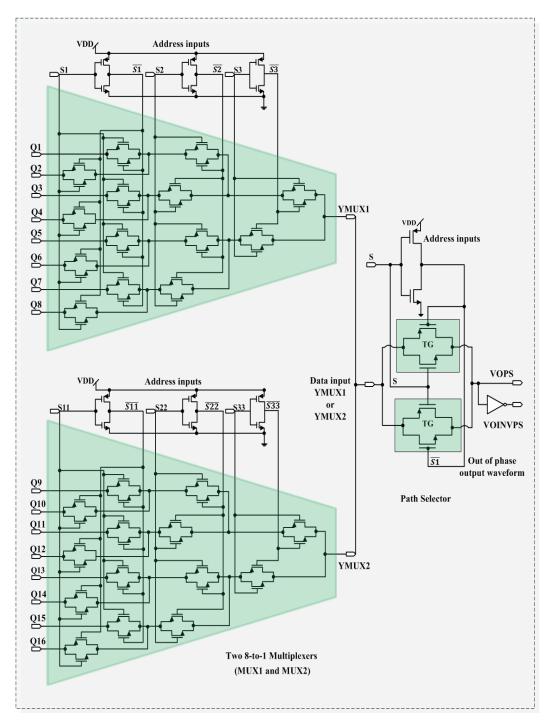

| 4.4.2.3 Multiplexors And Path Selector                               | 128 |

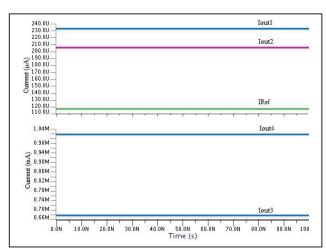

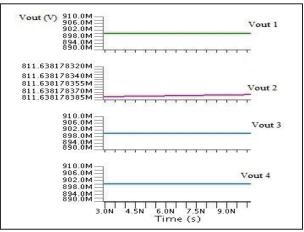

| 4.5 Simulation and Performance Analyses Of WFG <sub>INT</sub>        | 132 |

| 4.5.1 Robustness of The WFG <sub>INT</sub> Circuit                   | 135 |

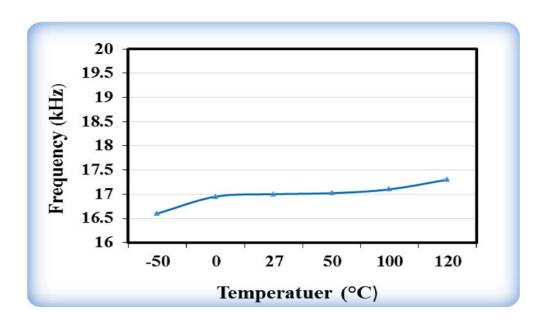

| 4.5.1.1 Temperature Variation                                        | 135 |

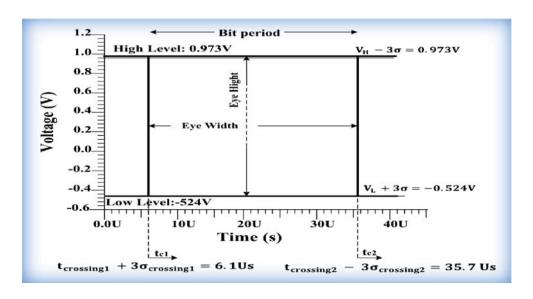

| 4.5.1.2 Eye Diagram Analysis                                         | 135 |

| 4.6 Simulation Results of The Digital Model                          | 137 |

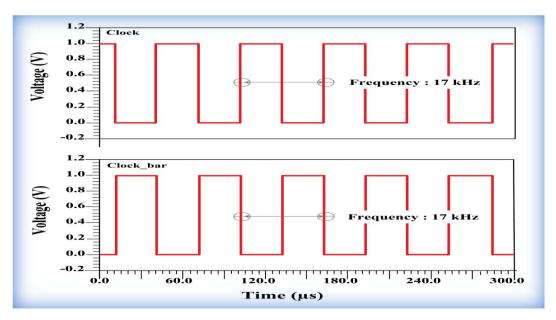

| 4.6.1 Clock And Clock_Bar                                            | 139 |

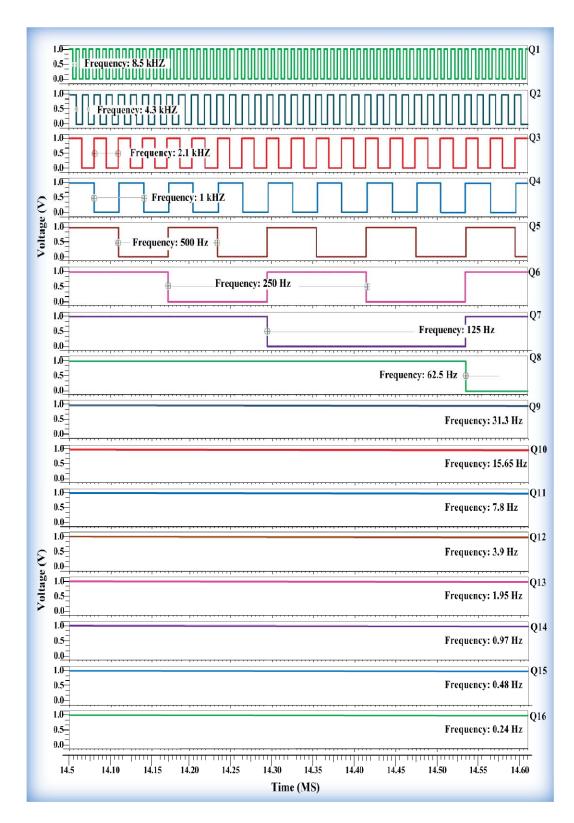

| 4.6.2 FD circuit                                                     | 140 |

| 4.7 Layout and Fabrication of The WFG <sub>INT</sub>                 | 146 |

| 4.8 Experimental Results of The WFG <sub>INT</sub>                   | 150 |

| 4.8.1 Amplitude Control of The WFG <sub>ING</sub>                    | 154 |

| 4.8.2 Frequency Control of The WFG <sub>ING</sub>                    | 155 |

| 4.9 Optimization Flowchart of The WFG <sub>ING</sub>                 | 159 |

| 4.10 Comparison of The WFG $_{\rm INT}$ With ELF WFG and With        |     |

| Other Published WFG                                                  | 161 |

| 4.11 Conclusion.                                                     | 163 |

| Chapter 5. Design Criteria, Implementation and Fabrication of a Low- |     |

| Power CMOS Active-Electrode-Pair For Low-Frequency Multi-            |     |

| Channel Biomedical Stimulation                                       | 165 |

| 5.1 Introduction                                                     | 165 |

| 5.2 Design Criteria for Active Electrode                             | 169 |

| 5.3 Circuit Design and Topology of The Active Electrode              | 170 |

|           | 5.3        | 3.1 Active Electrode Circuit Analysis                       | 17 |

|-----------|------------|-------------------------------------------------------------|----|

|           | 5.4        | Simulation And Performance Analyses of The Active           |    |

|           |            | Electrode                                                   | 17 |

|           | 5.5        | Layout and Fabrication of The Active Electrode              | 17 |

|           | 5.5        | 5.1 Experiment Results of The Active Electrode              | 18 |

|           | 5.6        | Conclusion.                                                 | 18 |

| Chapter 6 | . In V     | itro Biological Experiment Design And Performance To        |    |

|           | Inve       | estigate The Effect of Low Frequencies Electrical Pulses on |    |

|           | The        | Human Blood Cells                                           | 18 |

|           | 6.1        | Introduction                                                | 18 |

|           | 6.2        | Chemokine Receptor CCR5                                     | 13 |

|           | 6.2        | 2.1 CCR5 Protein Structure                                  | 19 |

|           | 6.3        | The Nuclear pore complex (NPC)                              | 1  |

|           | 6.4        | Frequency–Dependent Polarization                            | 2  |

|           | 6.5        | In Vitro Biological Tests                                   | 2  |

|           | 6.5        | 5.1 Materials and Procedure                                 | 2  |

|           | 6.5        | 5.2 Electrical Simulation Procedure                         | 2  |

|           | 6.5        | 5.3 Immunofluorescence Microscopy Assay                     | 2  |

|           |            | 6.5.3.1 Immunofluorescence Cell Staining Procedure          | 2  |

|           | 6.6        | Electrical Stimulation Results                              | 2  |

|           | 6.0        | 6.1 Expression of CD4 and CCR5                              | 2  |

|           | 6.0        | 6.2 CCR5 N-Terminal Conformation Epitopes                   | 2  |

|           | 6.0        | 6.3 Distribution of FGNup153                                | 2  |

|           | 6.7        | Discussions on Experimental Results                         | 2  |

|           | 6.8        | Conclusion                                                  | 2  |

| Chapter 7 | . Con      | clusion                                                     | 2  |

|           | 7.1        | Summary                                                     | 2  |

|           | 7.2        | Contributions of This Doctoral Research                     | 2  |

|           | 7.3        | Recommendations for Future Research                         | 2  |

| Reference | <b>S</b> 2 |                                                             | 2  |

| Appendix A. | <b>Supplementary Documents</b> | 282 |

|-------------|--------------------------------|-----|

|             | Ethic Approval                 | 283 |

|             | List of Publications           | 284 |

### **List of Abbreviations**

AA Amino Acid

Ab Antibody

D Aspartic Acid

BJT Bipolar Technology

BSA Bovine Serum Albumin

CCII Current Conveyor

CFOA Current Feedback Operational Amplifier

Clk Clock

Clk\_bar Clock\_bar

CM Current-Mode

CSE Clocked Storage Element

D-Flip Flop

DRC Design Rule Checking

ELF Extra Low Frequency

FBS Fetal Bovine Serum

FD Frequency Divider

FF Flip Flop

FG Phenylalanine-Glycine

h Hour

HCl Hydrochloric acid

HIV-1 Human immunodeficiency virus

IC Integrated Circuit

Kap Karyopherin

LVS Layout Versus Schematic

mAbs Monoclonal Antibodies

min Minute

MLF Moderate Low Frequency

MUX Multiplexer

NES Nuclear Export Signal

NLS Nuclear Localization Signal

nm Nano-metric

NPC Nuclear pore complex

Op-Amp Operational Amplifier

OTA Operational Trans-conductance Amplifiers

PFA Paraformaldehyde

PG Pass Gate

PIC Pre-Integration Complex

PS Path Selector

PVT Process And Temperature Variation

Q Glutamine

SC Stratum Corneum

SDL Schematic-Driven Layout

ST Schmitt Trigger

STG Stage

TG Transmission-Gate

TGFF Transmission-Gate Flip Flop

VTC Voltage Transfer Characteristic

WFG Waveform Generator

WFG<sub>INTG</sub> Waveform Generator Based on Integrator Timing Network

Y Tyrosine

## **List of Symbols**

| A                   | Area                           | Meter Square               |

|---------------------|--------------------------------|----------------------------|

| C                   | Capacitor                      | Farad                      |

| $C_{ox}$            | Gate oxide capacitance         | Farad                      |

| gm                  | Trans-conductance              | Microampere/microvolt      |

| W                   | Channel width of the MOSFET    | Micro-meter                |

| L                   | Channel length of the MOSFET   | Micro-meter                |

| ro                  | Output resistance of MOSFET    | Ohms                       |

| μη                  | Electron mobility              | Meter square/Volts seconds |

| IB                  | Bias Current of MOSFET         | Microamperes               |

| ID                  | DC Drain current of MOSFET     | Microamperes               |

| $V_{C}$             | Capacitor Voltage Output       | Volts                      |

| VDD                 | Positive Supply Voltage        | Volts                      |

| $V_{\mathrm{INT}}$  | Integrator Voltage Output      | Volts                      |

| Vo                  | Output Voltage                 | Volts                      |

| VSS                 | Negative Supply Voltage        | Volts                      |

| $V_{GS}$            | Gate-source voltage of MOSFET  | Volts                      |

| $V_{LTH-}$          | Lower Threshold Voltage        | Volts                      |

| $V_{ST}$            | Schmitt Trigger Voltage Output | Volts                      |

| $V_{TH}$            | Threshold voltage              | Volts                      |

| $V_{\mathit{UTH}+}$ | Upper Threshold Voltage        | Volts                      |

| $V_{in}$            | Input Voltage                  | Volts                      |

| $V_{sat-}$          | Low Negative Saturation Level  | Volts                      |

| $V_{sat+}$          | High Positive Saturation Level | Volts                      |

| R                   | Resistor                       | Ohms                       |

| P                   | Power                          | Watts                      |

| f                   | Frequency                      | Hertz                      |

| τ                   | Time constant                  | Seconds                    |

| T                   | Time Period                    | Seconds                    |

| ω                   | Angular frequency              | Radians per second         |

# **List of Figures**

| Figure 1.1: | Schematic diagram representing the development of a variety of     |    |

|-------------|--------------------------------------------------------------------|----|

|             | implantable and non-invasive biomedical devices in the real        |    |

|             | world. These devices use the application of an electric field with |    |

|             | an appropriate electrical signal and specific waveform and         |    |

|             | frequency to be applied internally or externally to a particular   |    |

|             | area of the body, to treat a variety of disorders or disease       |    |

|             | conditions, and to improve patients' lives                         | 5  |

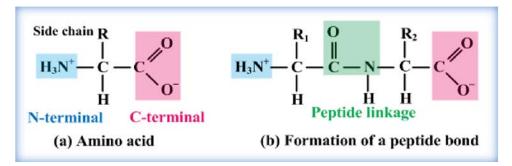

| Figure 1.2: | The primary protein structure, (a) amino acid structure, and (b)   |    |

|             | amino acids are connected together by a covalent linkage called a  |    |

|             | peptide bond to form polypeptide polymer chains and to build up    |    |

|             | the primary structure of a protein                                 | 10 |

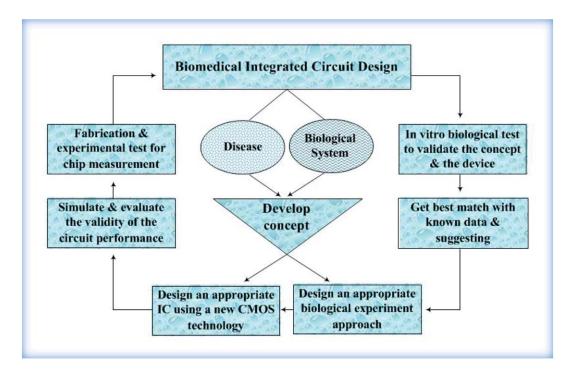

| Figure 1.3: | The development and design steps of electro-therapy concept and    |    |

|             | device of this research project, (a) block diagram, and (b)        |    |

|             | Schematic diagrams                                                 | 15 |

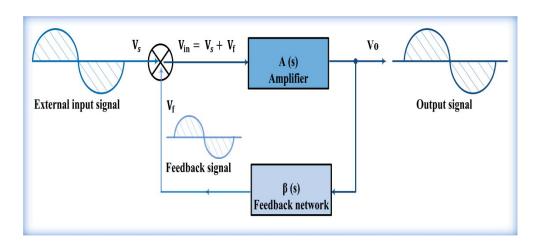

| Figure 2.1: | Block diagram of a simple positive feedback system                 | 27 |

| Figure 2.2: | Schematic diagram of a simple oscillatory system                   | 27 |

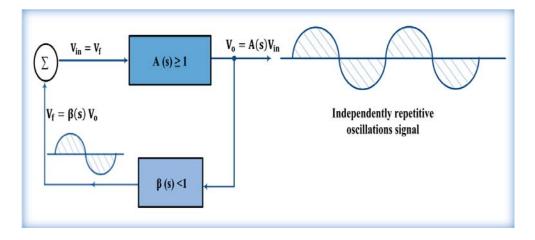

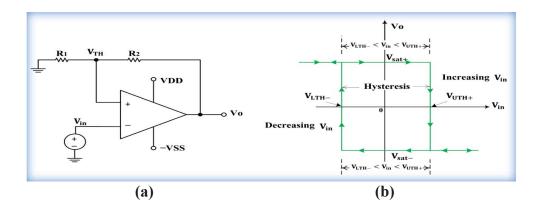

| Figure 2.3: | Schmitt Trigger, (a) basic Schmitt trigger circuit and (b) voltage |    |

|             | transfer characteristic of the Schmitt Trigger                     | 31 |

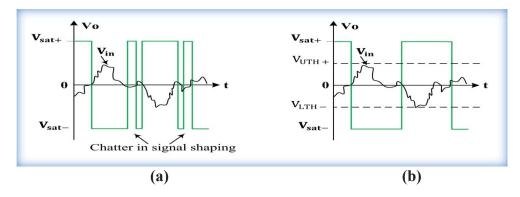

| Figure 2.4: | Comparison between the output voltage transfer characteristic of   |    |

|             | the comparator and the hysteresis Schmitt Trigger circuit, (a)     |    |

|             | comparator response to noisy signal, and (b) hysteresis Schmitt    |    |

|             | Trigger response to noisy signal                                   | 32 |

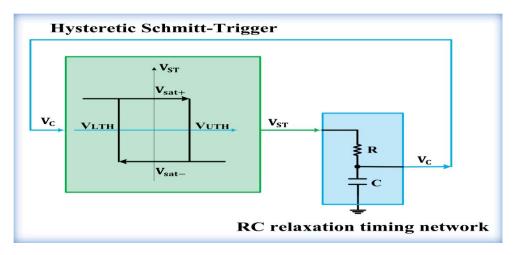

| Figure 2.5: | A basic block diagram of a typical WFG circuit, based on a RC      |    |

|             | relaxation timing network                                          | 34 |

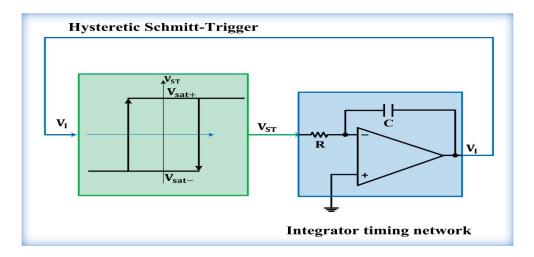

| Figure 2.6: | A basic block diagram of a typical WFG circuit based on a          |    |

|             | hysteretic Schmitt Trigger and an integrator relaxation timing     |    |

|             | network                                                            | 35 |

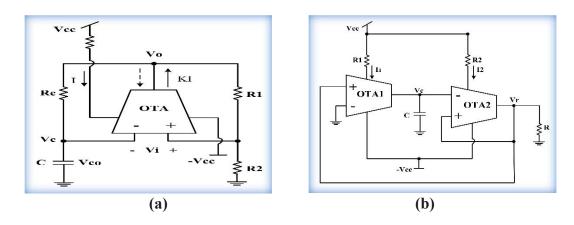

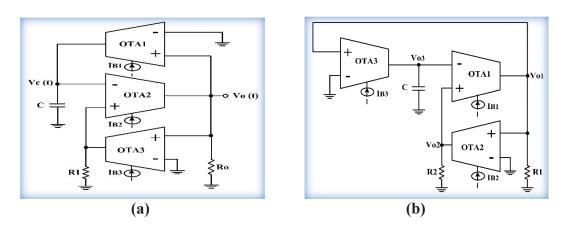

| Figure 2.7: | Waveform generator architectures based on, (a) single              |    |

|             | differential N-MOSFET OTA, (b) two differential N-MOSFET           |    |

|             | OTAs                                                               | 41 |

| Figure 2.8: | WFG architectures based on discrete LM3080 ICs OTAs and one        |    |

|              | comparator                                                          | 4 |

|--------------|---------------------------------------------------------------------|---|

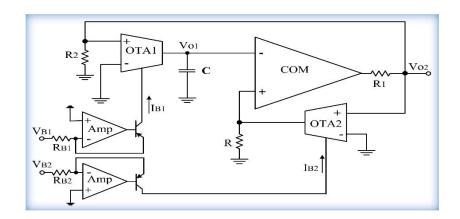

| Figure 2.9:  | WFG architectures based on one OTA and a two-stage                  |   |

|              | comparator                                                          | 4 |

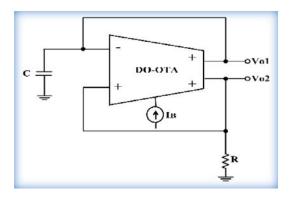

| Figure 2.10: | WFG architectures based on a dual output DO-OTA, using two          |   |

|              | single-ended commercial CA3080 OTA ICs                              | 4 |

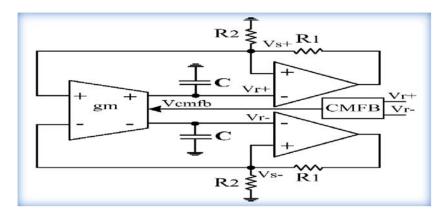

| Figure 2.11: | WFG architectures based on (a) three CMOS OTAs, (b) using           |   |

|              | three commercial available LM13600 ICs                              | 4 |

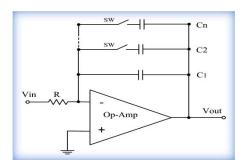

| Figure 2.12: | Op-Amp-RC integrator (a) first order Op-Amp-RC Integrator,          |   |

|              | (b) digitally controlled switched-capacitor matrices for tuning the |   |

|              | time constant of the Op-Amp-RC integrator circuit                   | 4 |

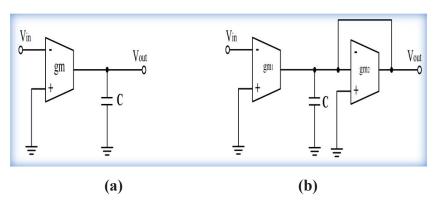

| Figure 2.13: | Gm-C integrator (a) first order integrator, (b) a lossy integrator  | 5 |

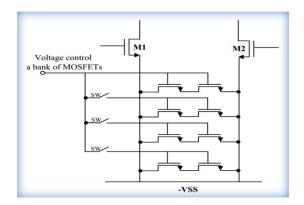

| Figure 2.14: | Resistive tuning techniques, voltage controls a bank of             |   |

|              | MOSFETs                                                             | 5 |

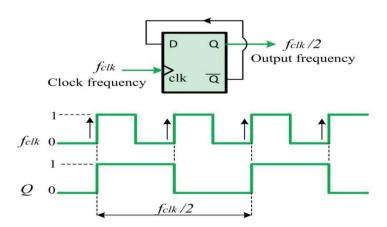

| Figure 2.15: | Schematic diagram of the frequency divider for "divide-by-2"        |   |

|              | (/2) frequency division circuit with its waveform output            | 5 |

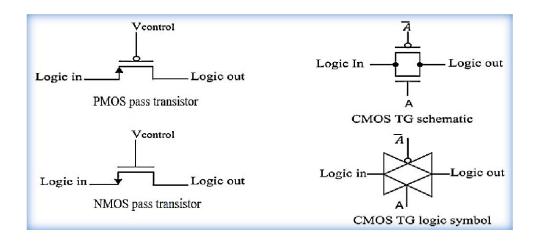

| Figure 2.16: | Schematic diagram of the logic gate (a) a simple PMOS and           |   |

|              | NMOS pass transistor and (b) a CMOS transmission gate and its       |   |

|              | logic symbol                                                        | 6 |

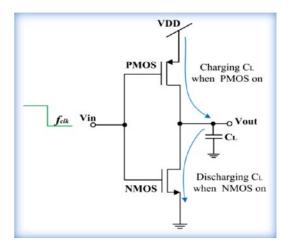

| Figure 2.17: | Schematic diagram of dynamic switching power dissipation in         |   |

|              | CMOS inverter                                                       | 6 |

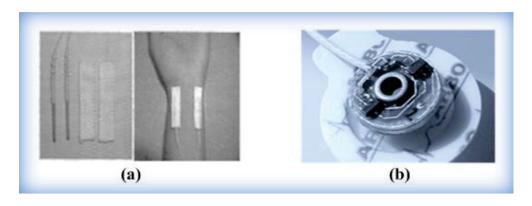

| Figure 2.18: | Types of electrodes: (a) passive electrodes, and (b), active        |   |

|              | electrode, using commercial Op-Amps with Ag/AgCl transducer         |   |

|              | for biomedical applications                                         | 6 |

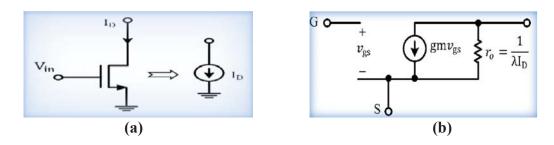

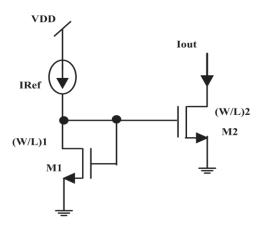

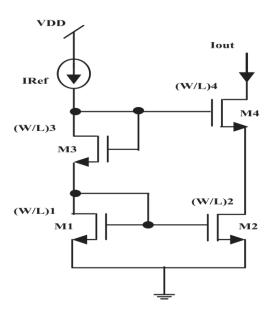

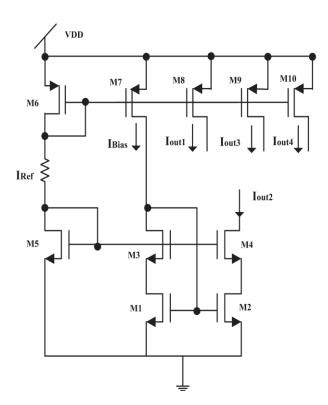

| Figure 3.1:  | Trans-conductance amplifier (a) a single common source              |   |

|              | MOSFET transistor operating in the saturation region as a           |   |

|              | current source, (b) the small-signal model                          | 7 |

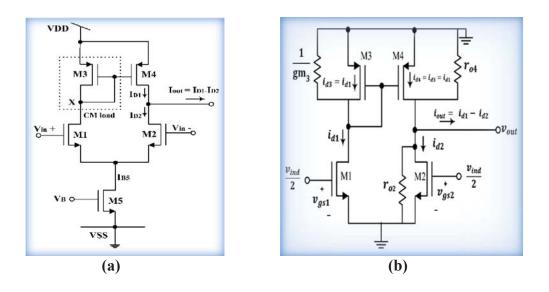

| Figure 3.2:  | CMOS Operational trans-conductance amplifier, (a) schematic         |   |

|              | diagram (b) the small signal model of the differential amplifier    |   |

|              | with a current mirror load                                          | 7 |

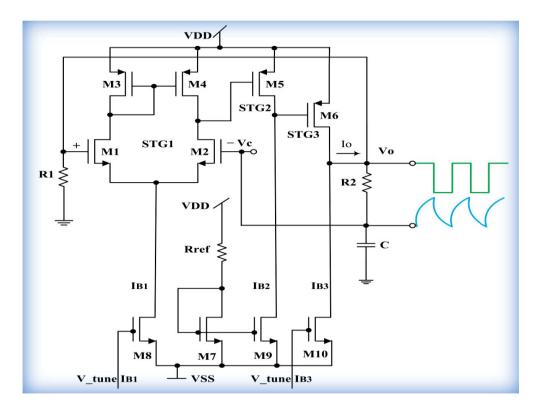

| Figure 3.3:  | Proposed, ELF WFG. Based on the periodical charging and             |   |

|              | discharging operation of the capacitor C, ELF WFG circuit,          |   |

|              | provides a periodical square waveform output signal at Vo and an    |   |

|              | exponential waveform at Vc with no input                            | 8 |

| Figure 3.4:  | Waveforms in the proposed ELF WFG                                   | 8.  |

|--------------|---------------------------------------------------------------------|-----|

| Figure 3.5:  | Simulated transient output waveforms for ELF WFG for the first      |     |

|              | design                                                              | 9   |

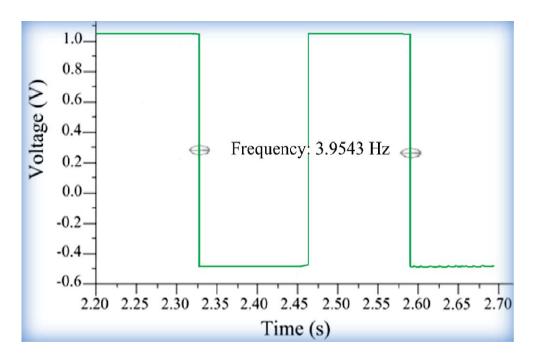

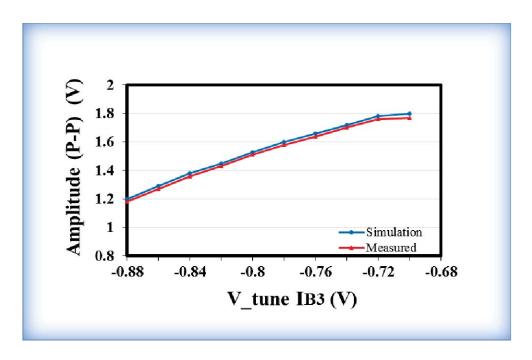

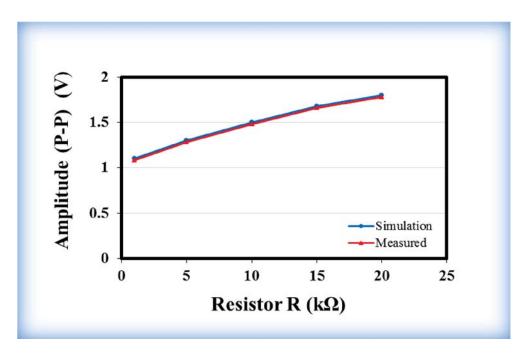

| Figure 3.6:  | Amplitude (P-P) variation with the bias current IB3 and resistor    |     |

|              | R1, (a) amplitude (P-P) variation with IB3 for the two ELF WFG      |     |

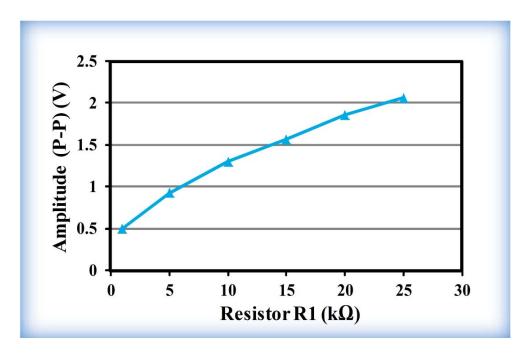

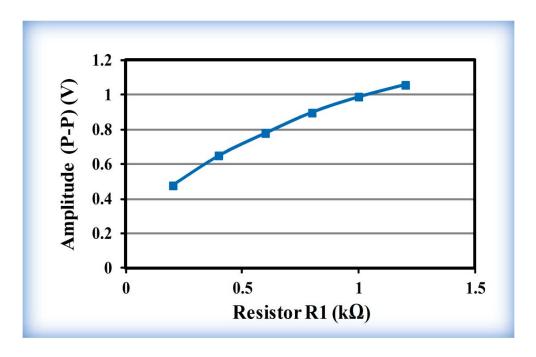

|              | designs, (b) amplitude (P-P) variation with R1 for the first design |     |

|              | and (c) amplitude (P-P) variation with R1 for the second            |     |

|              | design                                                              | 9.  |

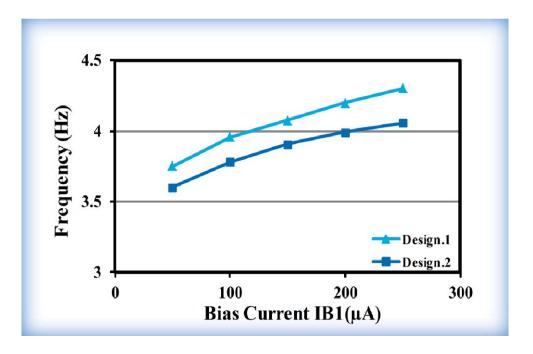

| Figure 3.7:  | Frequency tuning with bias current IB1 for the two ELF WFG          |     |

|              | designs                                                             | 94  |

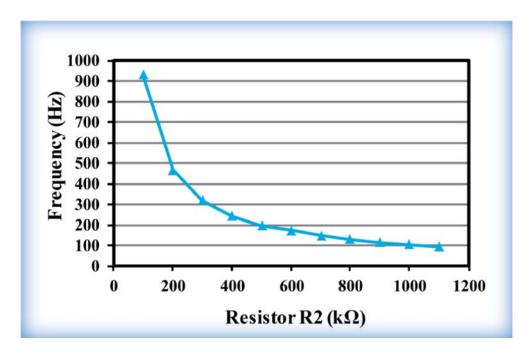

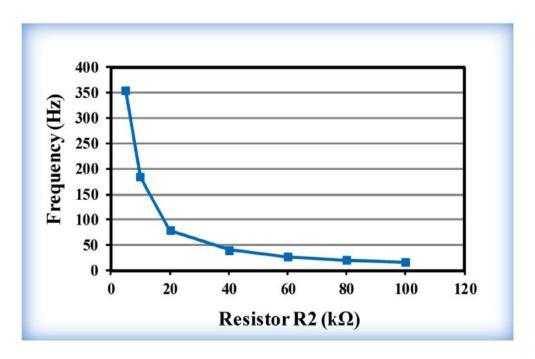

| Figure 3.8:  | Frequency tuning with resistor R2, (a) for the first ELF WFG        |     |

|              | design, (b) for the second ELF WFG design                           | 9:  |

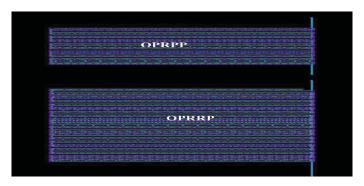

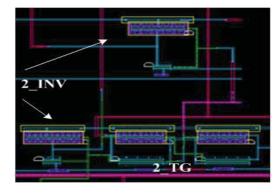

| Figure 3.9:  | The layout of on-chip identical units OPRPP and OPRRP               |     |

|              | resistors, in series                                                | 9′  |

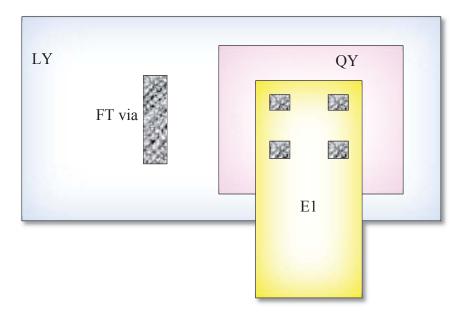

| Figure 3.10: | Layout for MIM capacitor                                            | 98  |

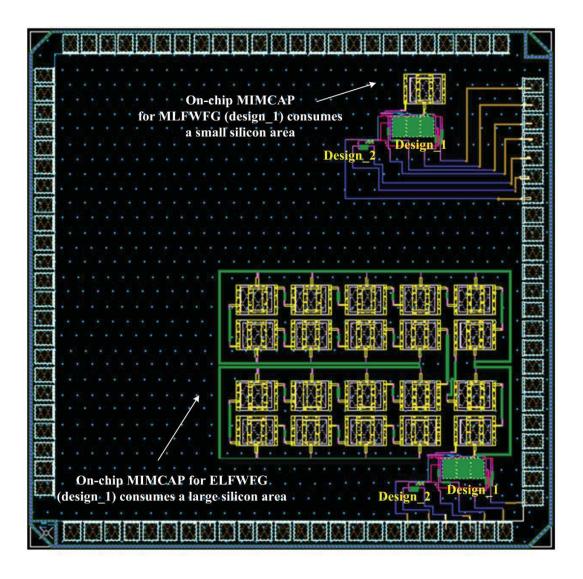

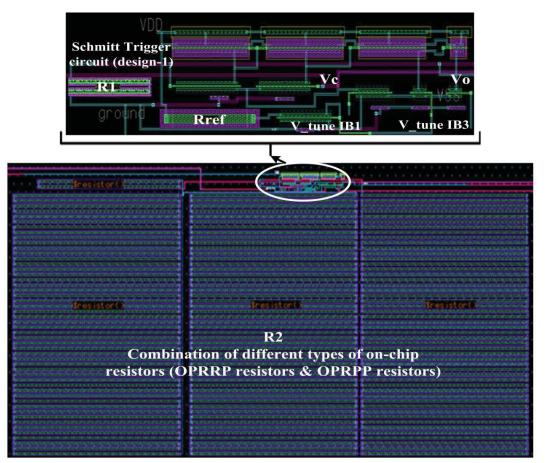

| Figure 3.11: | The layout for the two WFG circuit (design_1 and design_2).         |     |

|              | The layout on top right corner and bottom right corner represent    |     |

|              | the complete layout for the two WFG circuit including the on-       |     |

|              | chip designed MIMCAP for MLF WFG with 40pF, and for ELE             |     |

|              | WFG with 1nF for design _1 for area comparison                      | 100 |

| Figure 3.12: | A close view of the complete layout (excluding the capacitor) for   |     |

|              | the two ELF WFG circuit, for chip fabrication (a) for the first     |     |

|              | design, (b) for the second design. The top is the Schmitt Trigger   |     |

|              | circuit, while the rectangular box is the combination of different  |     |

|              | types of on-chip resistors                                          | 10  |

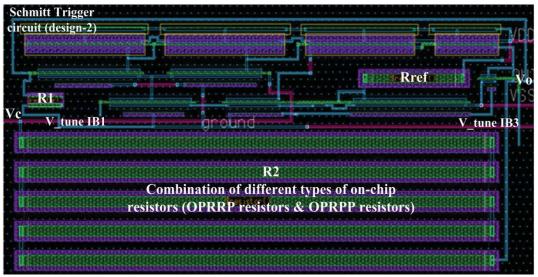

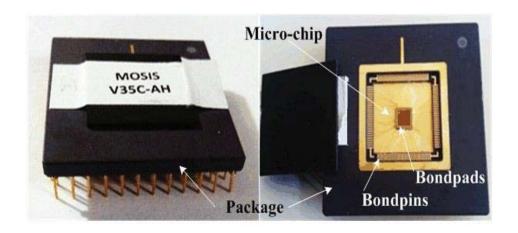

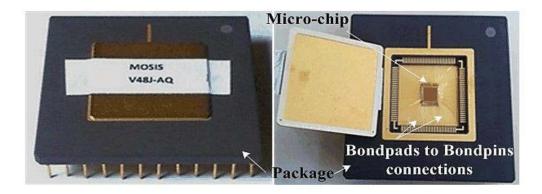

| Figure 3.13: | Package of the two ELF WFG circuit in PGA                           | 102 |

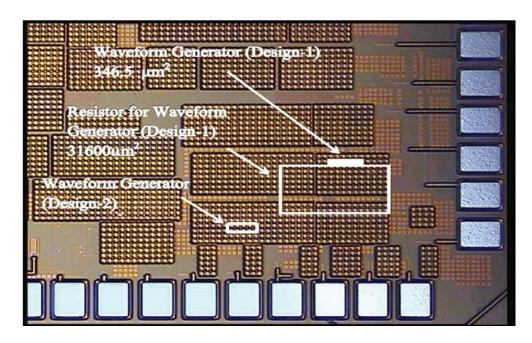

| Figure 3.14  | Chip photo-micrograph illustrates the location of the integrated    |     |

|              | two ELE WFG circuit                                                 | 102 |

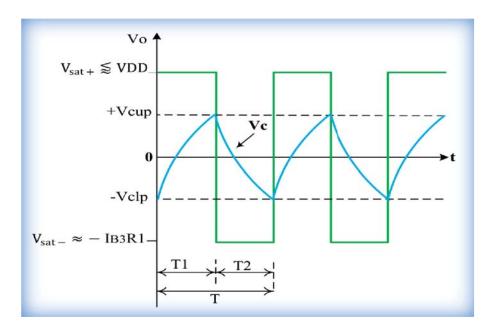

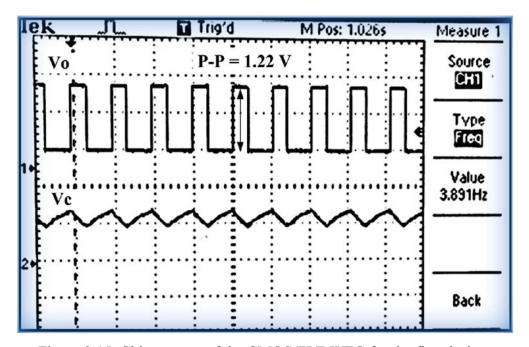

| Figure 3.15: | Chip outputs of the CMOS ELE WFG for the first design               | 10. |

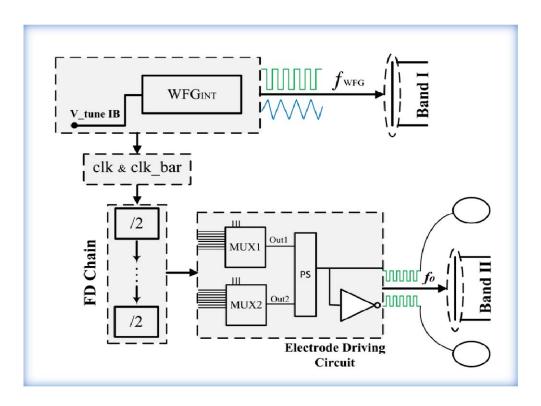

| Figure 4.1:  | Block diagram of the proposed mixed-signal CMOS waveform            |     |

|              | generator. Oscillation frequency of WFG core circuit is $f_{WFG}$   |     |

|              | (band I) and the digitally channelized selectable output frequency  |     |

|              | is $f_o$ (band II)                                                  | 10  |

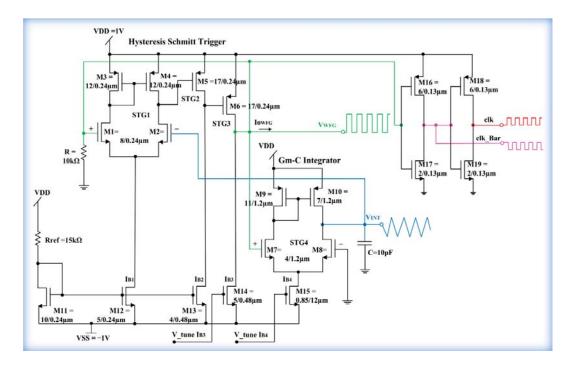

| Figure 4.2:  | A schematic diagram of the core square/triangular WFG <sub>INT</sub> based  |     |

|--------------|-----------------------------------------------------------------------------|-----|

|              | on gm-C integrator with clock and clock _bar generator                      | 112 |

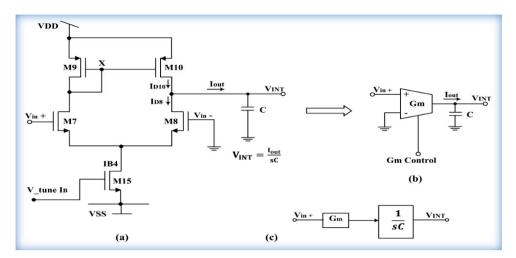

| Figure 4.3:  | A single stage gm-C integrator based on CMOS OTA, (a) circuit               |     |

|              | implementation, (b) integrator symbol and (c) building blocks               |     |

|              | diagram                                                                     | 113 |

| Figure 4.4:  | Schematic diagram of the WFG <sub>INT</sub> circuit operation, (a) transfer |     |

|              | characteristic of the Schmitt trigger design, and (b) the square            |     |

|              | and triangular waveforms of the designed WFG $_{\mathrm{INT}}$ circuit      | 117 |

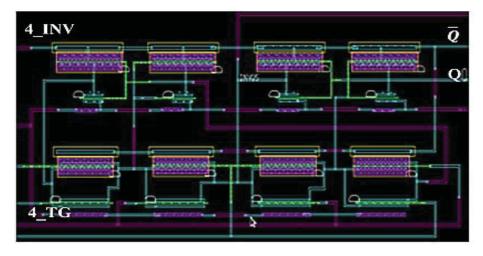

| Figure 4.5:  | The schematic diagram of the designed TGMS D-FF for a                       |     |

|              | divide-by/2 frequency division circuit                                      | 128 |

| Figure 4.6:  | The implementation of the designed TGMS D-FF for a divide-                  |     |

|              | by/2 frequency division circuit                                             | 128 |

| Figure 4.7:  | Multiplexers and path selector along with output driving circuit            | 130 |

| Figure 4.8:  | The complete architecture of the dual-band 16-channel mixed-                |     |

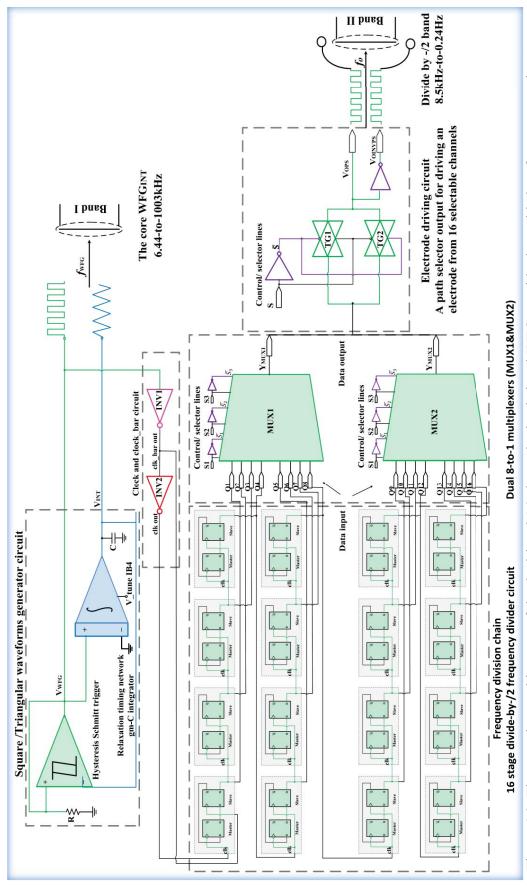

|              | signal WFG <sub>ING</sub> with ultra-wide low frequency tuning range        | 131 |

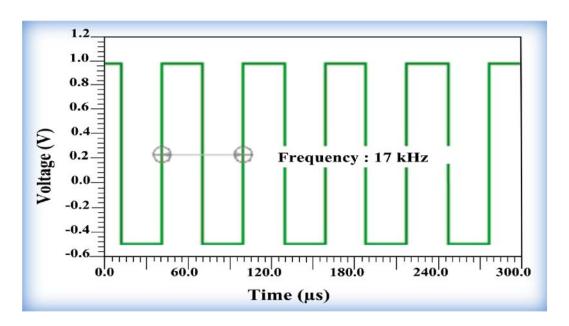

| Figure 4.9:  | Simulated transient square waveform output of the WFG <sub>INT</sub>        | 134 |

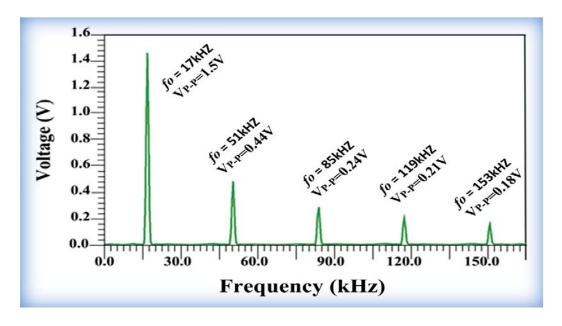

| Figure 4.10: | Spectrum analysis of the square waveform signal $(f_{WFG} = 17)$            |     |

|              | kHz) in simulation profile                                                  | 134 |

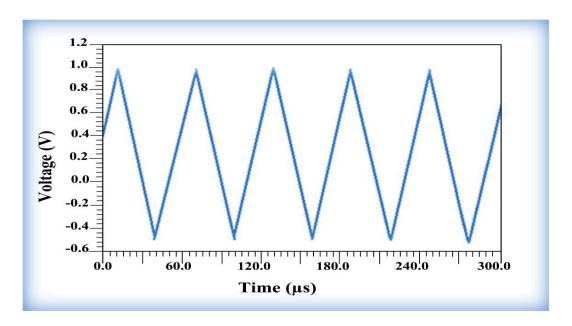

| Figure 4.11: | Simulated transient triangular waveform at the integrator output            | 135 |

| Figure 4.12: | WFG <sub>INT</sub> circuit analysis for the frequency stability with        |     |

|              | temperature variations                                                      | 137 |

| Figure 4.13: | Eye diagram simulation results for the designed $WFG_{INT}$                 | 137 |

| Figure 4.14: | Simulated transient response of the clock and clock_bar                     |     |

|              | generator                                                                   | 139 |

| Figure 4.15: | The 16 channel output square waveforms digitally selectable                 |     |

|              | through MUX1, MUX2 and PS                                                   | 141 |

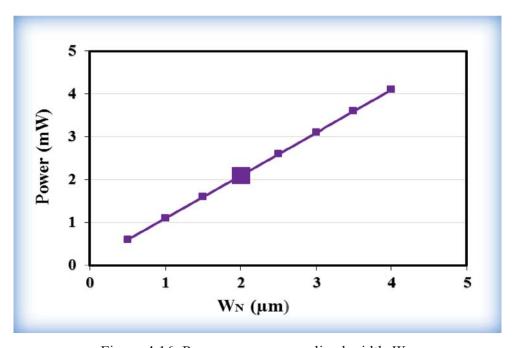

| Figure 4.16: | Power versus generalized width $W_N$                                        | 143 |

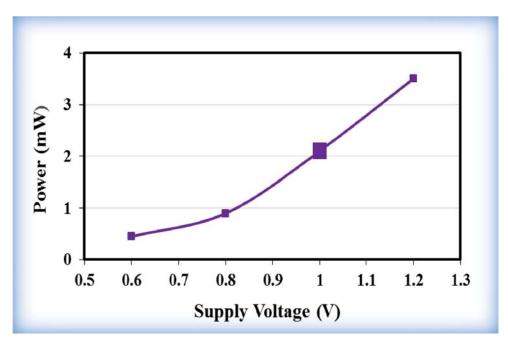

| Figure 4.17: | Power dissipation versus supply voltage of the FD circuit                   | 144 |

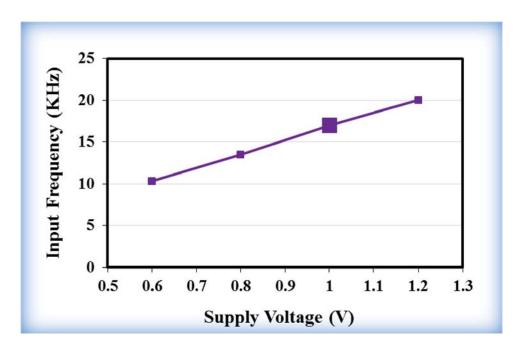

| Figure 4.18: | WFG <sub>ING</sub> frequency versus supply voltage                          | 144 |

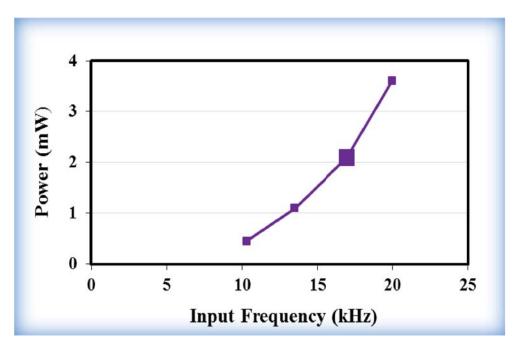

| Figure 4.19: | The simulated speed-power trade-off of the FD circuit                       | 145 |

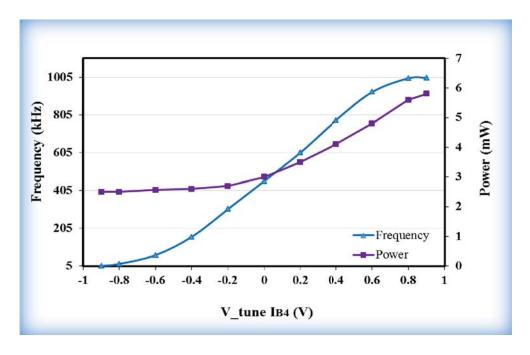

| Figure 4.20: | The simulation result for power and frequency versus V_tune                 | 145 |

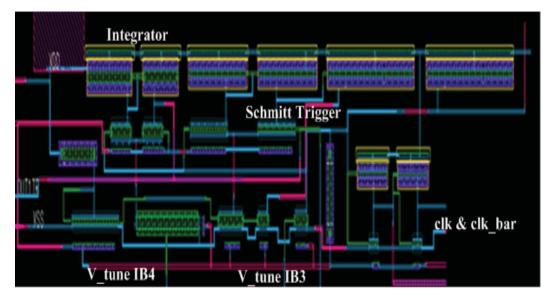

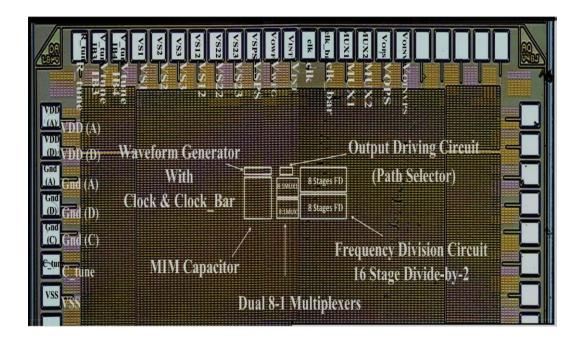

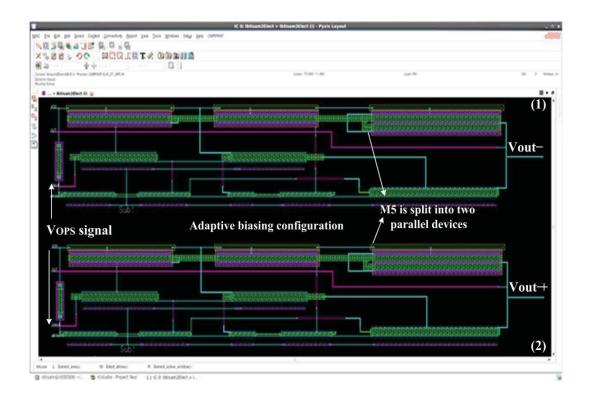

| Figure 4.21: | The complete layout (including the capacitor) for the (mixed-               |     |

|              | signal) dual-band WFG <sub>INT</sub> circuit, (a) the overall layout of the |     |

|              | mixed-signal WFG <sub>INT</sub> circuit, (b) show close views of the             |     |

|--------------|----------------------------------------------------------------------------------|-----|

|              | WFG <sub>INT</sub> core circuit, (c) D-FF, (d) MUX1, and (e) PS                  |     |

|              | circuit                                                                          | 149 |

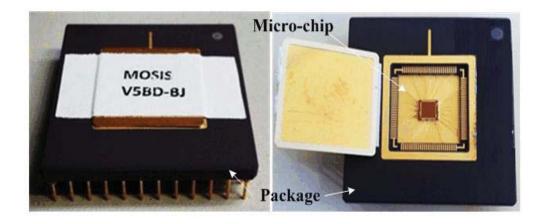

| Figure 4.22: | Package of the analog WFG <sub>INT</sub> and the digital model circuit in        |     |

|              | PGA                                                                              | 150 |

| Figure 4.23: | Chip photo-micrograph illustrates the location of the integrated                 |     |

|              | mixed-signal dual-band WFG <sub>INT</sub> circuit                                | 150 |

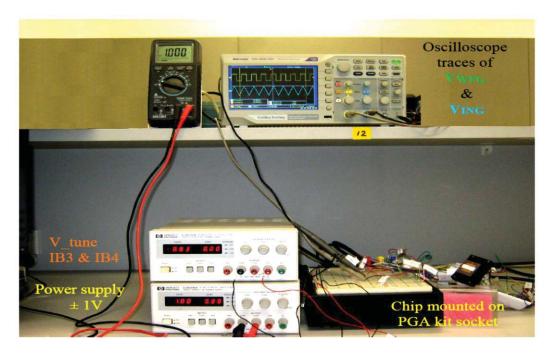

| Figure 4.24: | Experimental measurement set up for the fabricated oscillator                    | 151 |

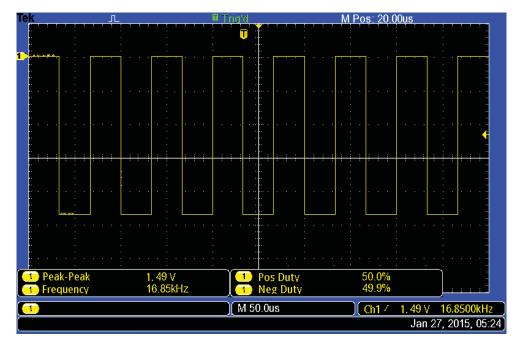

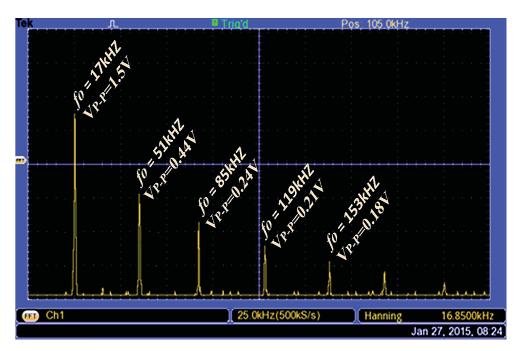

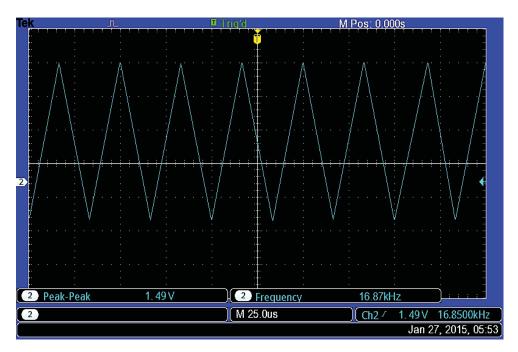

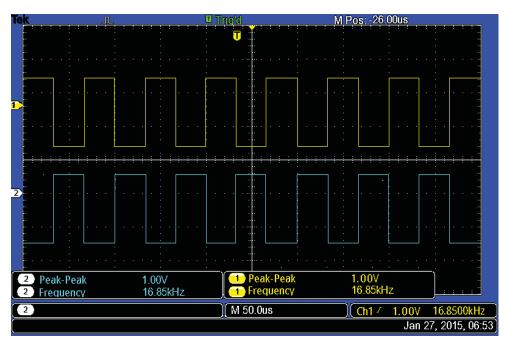

| Figure 4.25: | Measured chip outputs, (a) square waveform of the core WFG <sub>INT</sub> ,      |     |

|              | (b) FFT spectrum analysis of the generated square waveform                       |     |

|              | signal, (c) triangular waveform of the integrator, and (d) clock                 |     |

|              | and clock_bar translation outputs                                                | 153 |

| Figure 4.26: | Amplitude (P-P) variation comparing measured results and                         |     |

|              | simulation, (a) with V_tune bias current IB3, and, (b) with R.                   | 155 |

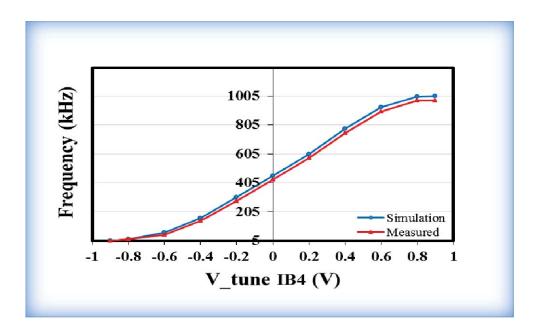

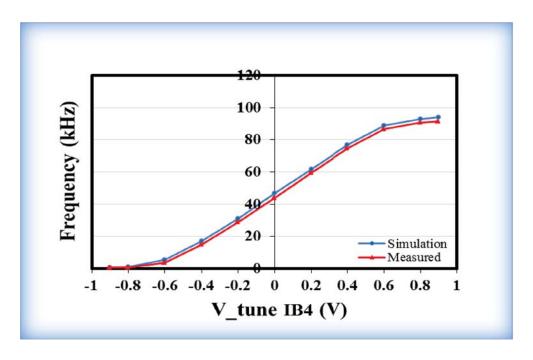

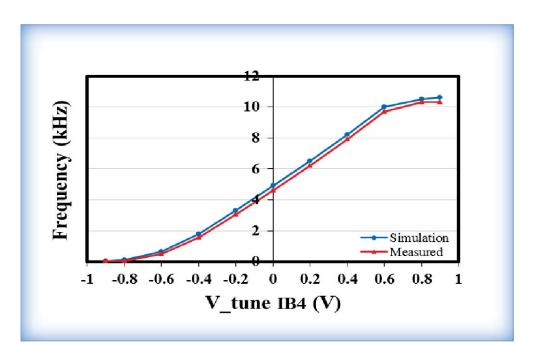

| Figure 4.27: | The measured profile values of the oscillation frequency vs. V-                  |     |

|              | tune of the WFG <sub>INT</sub> output signal, compared with the simulation       |     |

|              | profile values and the related results for 10 pF, 100 pF and 1000                |     |

|              | pF load capacitor values respectively                                            | 157 |

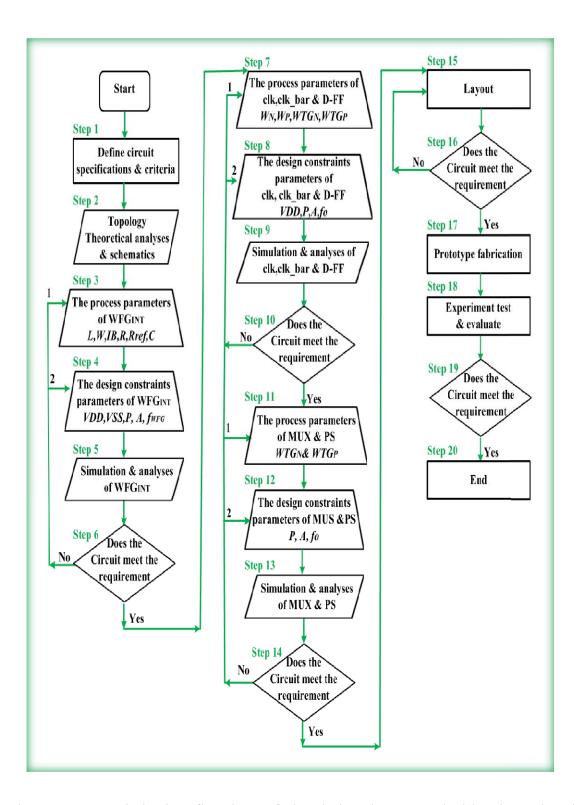

| Figure 4.28: | Optimization flowchart of the designed CMOS dual-band 16-                        |     |

|              | chanal mixed-signal waveform generator                                           | 160 |

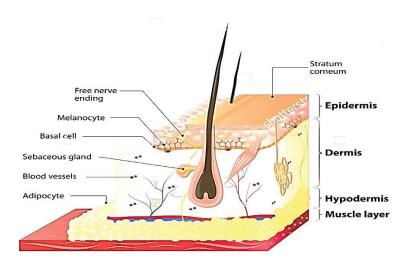

| Figure 5.1:  | Human skin layer                                                                 | 166 |

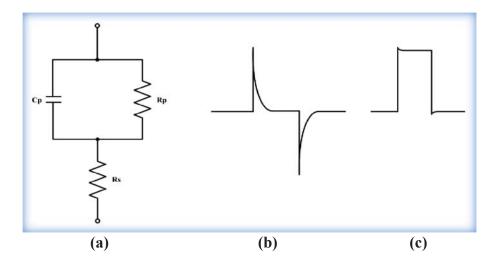

| Figure 5.2:  | Current response of skin to the application of a square-wave                     |     |

|              | voltage pulse                                                                    | 167 |

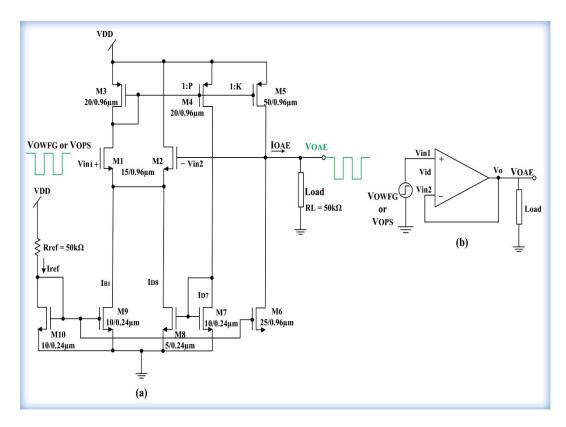

| Figure 5.3:  | Proposed adaptive biased CMOS active electrode circuit, (a)                      |     |

|              | circuit implementation, with input stage bias current set                        |     |

|              | dynamically by two mechanisms, first, by the simple current                      |     |

|              | mirror and secondly, by applying adaptive biasing, and (b)                       |     |

|              | equivalent circuit representing the voltage follower active                      |     |

|              | electrode circuit.                                                               | 170 |

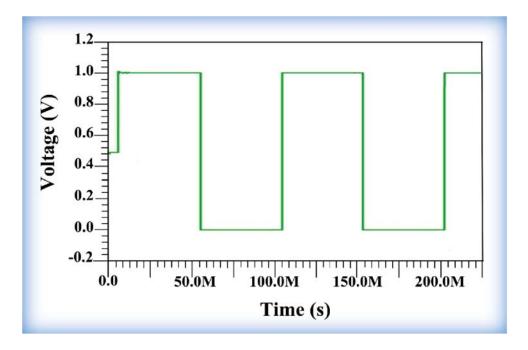

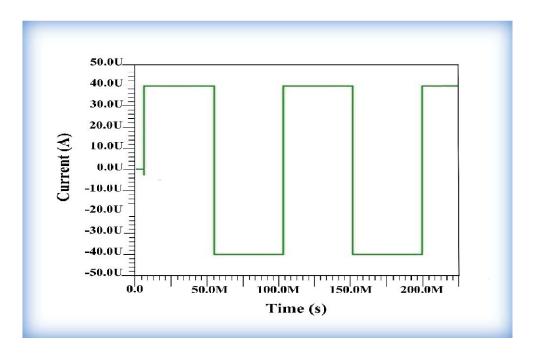

| Figure 5.4:  | Simulated transient response of individual active electrode buffer               |     |

|              | to an input square-wave pulse of a 100ms duration and +1V                        |     |

|              | amplitude (the $V_{OPS}$ output of the PS in chapter 4) for $RL=50$ k $\Omega$ . | 175 |

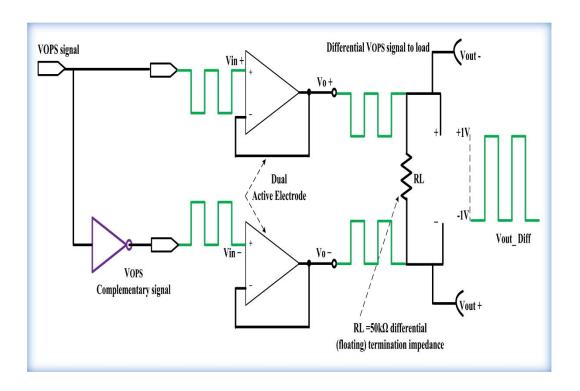

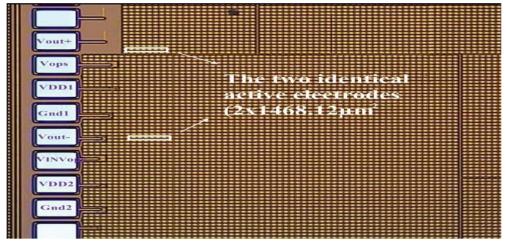

| Figure 5.5:  | The configuration for bio-potentials signals application,                        |     |

|              | employing two identical active electrodes                                    | 177 |

|--------------|------------------------------------------------------------------------------|-----|

| Figure 5.6:  | Simulated transient response of the dual active electrode circuit            |     |

|              | driving a $50k\Omega$ floating load in a differential fashion displaying a   |     |

|              | transmitted bi-phase square waveform with, (a) approximately $\pm$           |     |

|              | 1V differential output voltage, and (b) $\pm$ 40 $\mu$ A differential output |     |

|              | current                                                                      | 178 |

| Figure 5.7:  | The two identical active electrode circuits (a) layout, (b) package          |     |

|              | of the microchip and (c) Chip photo-micrograph of the fabricated             |     |

|              | die                                                                          | 180 |

| Figure 5.8:  | Experimental set-up for the active electrode chip output                     |     |

|              | waveform measurements                                                        | 18  |

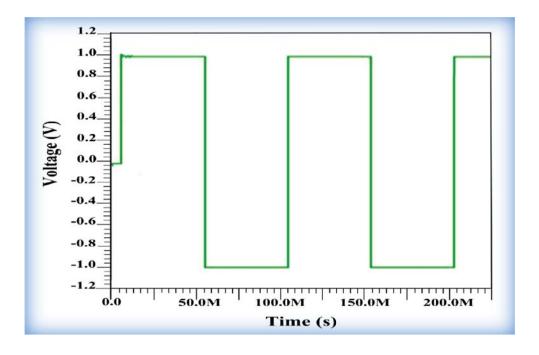

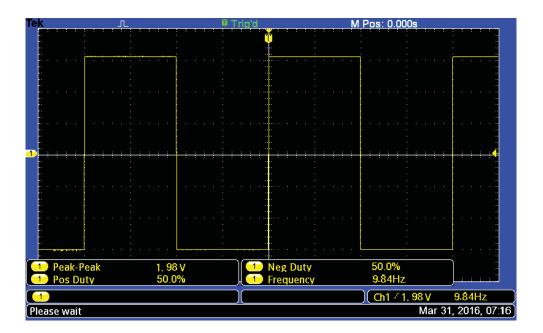

| Figure 5.9:  | Oscilloscope trace of the differential output waveform signal of             |     |

|              | the dual identical active electrode circuits                                 | 18  |

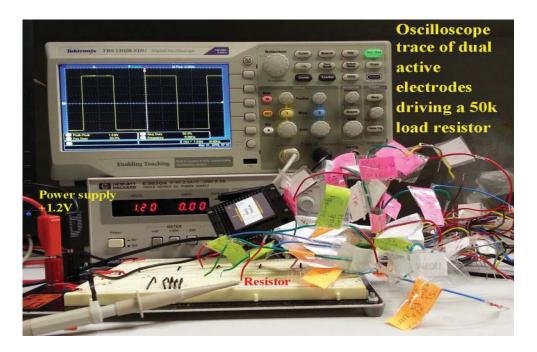

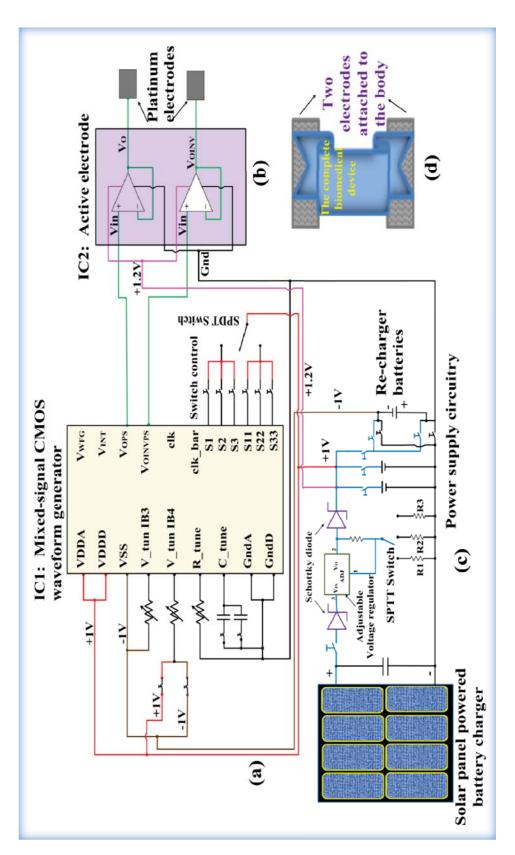

| Figure 5.10: | A proposed proto-type electro-bio-stimulation system using the               |     |

|              | fabricated active electrode-pair complete with (a) mixed-signal              |     |

|              | CMOS waveform generator, WFG <sub>ING</sub> (IC1 in chapter 4), (b) the      |     |

|              | active electrode-pair (IC2), and, (c) solar panel charged regulated          |     |

|              | power-supply. The complete encapsulated bio-medical device                   |     |

|              | with electrode contacts is shown in (d)                                      | 184 |

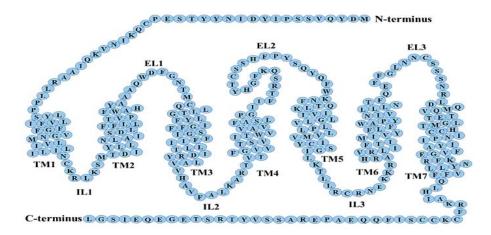

| Figure 6.1:  | Protein structure of co-receptor CCR5 and its sequence. The                  |     |

|              | image outlines the residues of N-terminus, and C-terminus,                   |     |

|              | residues of the 7-TM region and of the extracellular (EL) and                |     |

|              | intracellular loop (IL) regions respectively                                 | 190 |

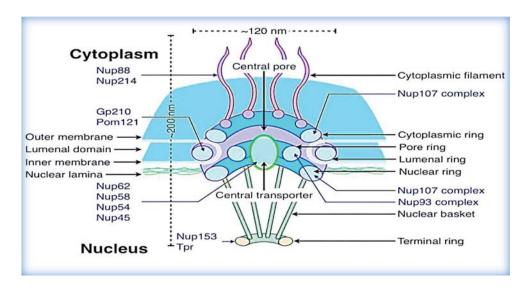

| Figure 6.2:  | Nuclear pore complex structure                                               | 19: |

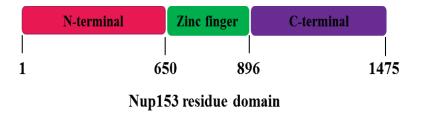

| Figure 6.3:  | A heterogeneous tripartite structure of FGNup153, comprises                  |     |

|              | three different domains, N-terminal domain, zinc finger domain,              |     |

|              | and C-terminal domain                                                        | 19  |

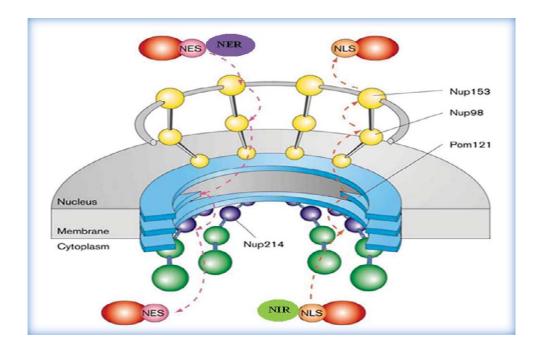

| Figure 6.4:  | Nuclear pore complex model for protein import and export of                  |     |

|              | large macromolecular proteins that are recognized by nuclear                 |     |

|              | transport receptors (NTRs) and passage them through the central              |     |

|              | channel                                                                      | 20  |

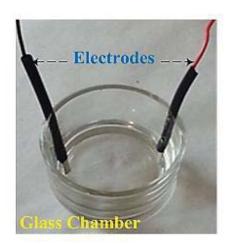

| Figure 6.5:  | The electrical test glass chamber with stainless steel wire                  | 20  |

|              | electrodes                                                                   |     |

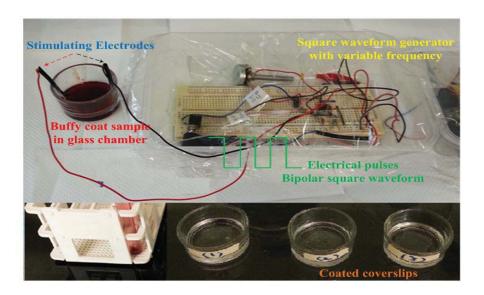

| Figure 6.6:  | Experimental set up for electrical stimulation test. Healthy       |     |

|--------------|--------------------------------------------------------------------|-----|

|              | human buffy coat samples were exposed for 2h to low frequency      |     |

|              | bipolar square waveform pulses of 5Hz, 10Hz and 1000kHz with       |     |

|              | 1Vpp in a 30ml capacity glass chamber, 3cm in diameter, with       |     |

|              | stainless steel wire electrodes                                    | 207 |

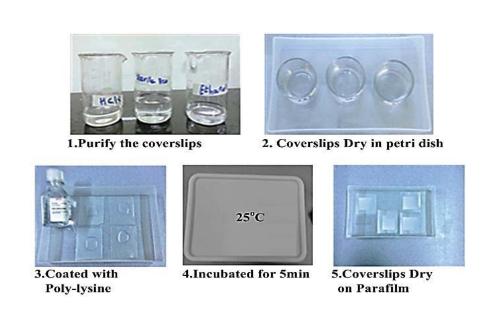

| Figure 6.7:  | Purifying and coating coverslips with HCl and poly-lysine          |     |

|              | respectively, to assure cells adhesion                             | 208 |

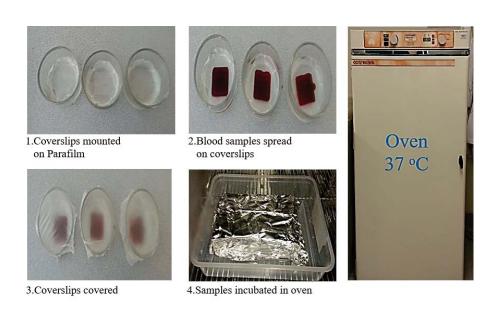

| Figure 6.8:  | Cells adhesion on coverslips. Buffy coat samples spread and        |     |

|              | plated on coated coverslips that are mounted on Parafilm to        |     |

|              | prevent the coverslips from moving, and then incubated in oven     |     |

|              | for 30 min at 37 °C                                                | 209 |

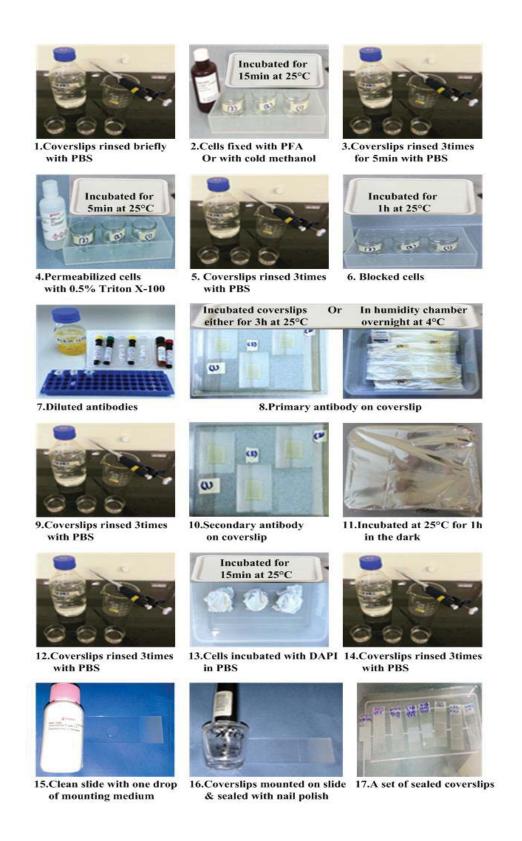

| Figure 6.9:  | The steps of experimental procedure for immunofluorescence         |     |

|              | cells staining                                                     | 212 |

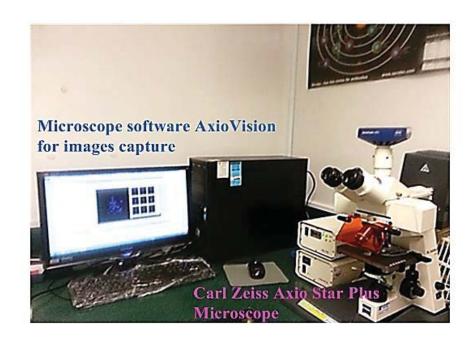

| Figure 6.10: | Experimental setup for acquiring images. (a) A Carl Zeiss Axio     |     |

|              | Star plus microscope with AxiosVison software, and (b) the         |     |

|              | tested and most successful sealed coverslips used in this          |     |

|              | experiment                                                         | 213 |

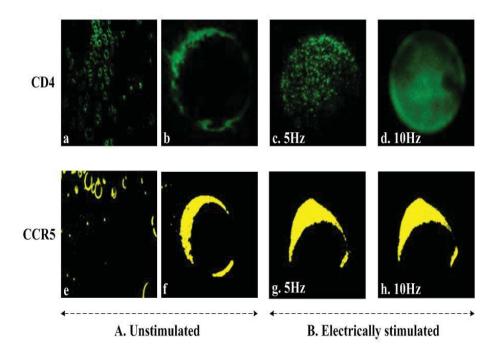

| Figure 6.11: | Cell surface expression of CD4 (green) and CCR5 (yellow) in        |     |

|              | human healthy buffy coat samples, for unstimulated (A) cells and   |     |

|              | for electrically stimulated cells (B) in response to low frequency |     |

|              | electrical simulation conditions of 5Hz and 10Hz with 1V for 2h,   |     |

|              | analysed by immunofluorescence microscope. The intensity and       |     |

|              | distribution of the fluorescence on the cell membrane and cell     |     |

|              | surface represents the concentration of CD4 expression and         |     |

|              | CCR5 expression for unstimulated cells as shown in (b) and (f),    |     |

|              | and for electrically stimulated cells of 5Hz and 10Hz as shown in  |     |

|              | (c), (d), (g) and (h) respectively. (a) and (b) images display a   |     |

|              | wider view of the CD4 and CCR5 cell populations                    | 215 |

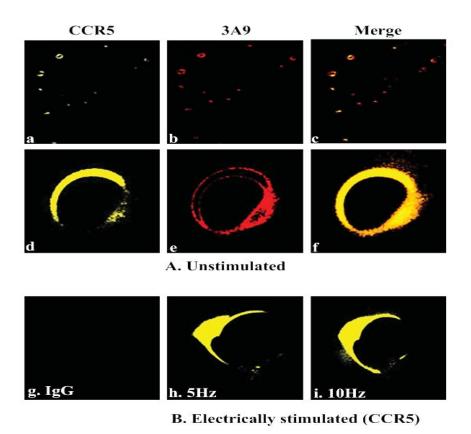

| Figure 6.12: | Immunofluorescence assay for cellular distribution and binding     |     |

|              | activity of the healthy human CCR5 receptor. Leukocyte-rich        |     |

|              | buffy coat cells were assayed with mAb 3A9 followed by Alexa       |     |

|              | Fluora 555 labelled goat anti-mouse IgG directed against the N-    |     |

|              | terminal domain of CCR5 to study the binding activities of 3A9     |     |

|              | ·                                                                  |     |

| epitope in this region, in response to a low frequency electrical     |                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| field. The images (a), (b) and (c) show a wider view of the cell      |                                                                                                                                                                                                                                                                                                                                                                   |

| population, the binding activity of unstimulated cells (A), CCR5      |                                                                                                                                                                                                                                                                                                                                                                   |

| (yellow) in (d) with 3A9 (red) in (e) is shown in orange (merge)      |                                                                                                                                                                                                                                                                                                                                                                   |

| in (f), while (g) represents IgG as a control, (h) and (i) represents |                                                                                                                                                                                                                                                                                                                                                                   |

| the CCR5 (yellow) in response to electrical stimulation (B) of        |                                                                                                                                                                                                                                                                                                                                                                   |

| 5Hz and 10Hz respectively                                             | 217                                                                                                                                                                                                                                                                                                                                                               |

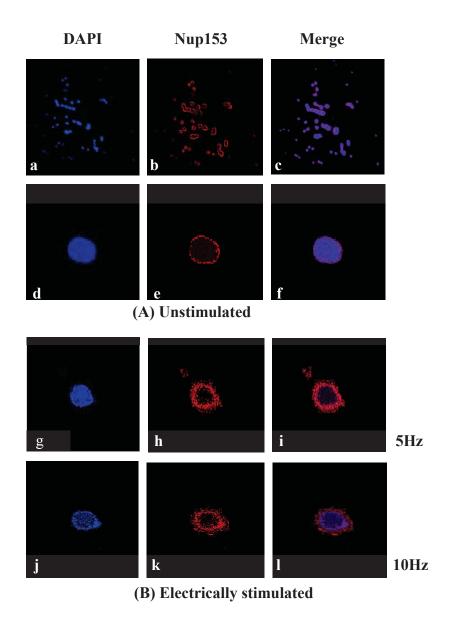

| The immunofluorescence microscope images of the distribution          |                                                                                                                                                                                                                                                                                                                                                                   |

| and pattern of the FGNup153. The images DAPI (blue) in (a) and        |                                                                                                                                                                                                                                                                                                                                                                   |

| (d) with Nup153 (red) in (b) and (e) is shown in purple (merge)       |                                                                                                                                                                                                                                                                                                                                                                   |

| in (c) and (f), displaying a wider view of the cell population for    |                                                                                                                                                                                                                                                                                                                                                                   |

| unstimulated cells (A) respectively. The co-localization of           |                                                                                                                                                                                                                                                                                                                                                                   |

| FGNup153 with mAb for (B) cells electrically stimulated with          |                                                                                                                                                                                                                                                                                                                                                                   |

| 5Hz and 10Hz incubated for 15min at -20°C in cold 100%                |                                                                                                                                                                                                                                                                                                                                                                   |

| methanol are displayed in (g), (h), (i) and (j), (k), and (l),        |                                                                                                                                                                                                                                                                                                                                                                   |

| respectively. For cells stimulated with 5Hz and 10Hz (green) that     |                                                                                                                                                                                                                                                                                                                                                                   |

| were fixed in 4% PFA and permeabilized by incubating for 5 min        |                                                                                                                                                                                                                                                                                                                                                                   |

| at room temperature with 0.5% Triton X-100 the data is not            |                                                                                                                                                                                                                                                                                                                                                                   |

| shown                                                                 | 222                                                                                                                                                                                                                                                                                                                                                               |

|                                                                       | field. The images (a), (b) and (c) show a wider view of the cell population, the binding activity of unstimulated cells (A), CCR5 (yellow) in (d) with 3A9 (red) in (e) is shown in orange (merge) in (f), while (g) represents IgG as a control, (h) and (i) represents the CCR5 (yellow) in response to electrical stimulation (B) of 5Hz and 10Hz respectively |

### **Lists of Tables**

| Table 2.1: | A comparison between capacitor values and corresponding kT/C          |     |

|------------|-----------------------------------------------------------------------|-----|

|            | noise                                                                 | 47  |

| Table 3.1: | Transistor dimensions for the two ELF WFG designs (1 and 2)           | 89  |

| Table 3.2: | Component values for the two ELF WFG designs (1 and 2)                | 89  |

| Table 3.3: | Comparison of the simulation performance of the first ELF WFG         |     |

|            | design (design 1) with the second ELF WFG design (design 2)           | 91  |

| Table 4.1: | The power and area versus generalized transistor width for the        |     |

|            | designed FD circuit.                                                  | 143 |

| Table 4.2: | Simulation results of the outputs of the dual band WFG <sub>INT</sub> |     |

|            | designed circuit                                                      | 146 |

| Table 4.3: | The tuning range of the oscillator frequency for the $WFG_{INT}$ core |     |

|            | (band I) for C=10pF, with V-tune varied from $-0.9V$ to $+0.9V$ ,     |     |

|            | and the equivalent oscillator frequency the circuit can provide,      |     |

|            | with 16 channel FD circuit (band II)                                  | 158 |

| Table 4.4: | Comparison of the proposed WFG <sub>INT</sub> with ELF WFG of this    |     |

|            | work and with some other solutions in the reported literature         | 162 |

| Table 5.1: | Performance and comparison of the proposed active electrode           |     |

|            | with the previous reported                                            | 183 |

### Chapter 1

### Introduction

### 1.1 Biomedical Integrated Circuit Design

There is a growing demand for technological improvement in healthcare. There have been promising developments in Biomedical Integrated Circuit (IC) design for a variety of low-cost, and light-weight bioelectronics circuit solutions, for batteryoperated biomedical devices. Biomedical integrated circuit design is emerging as a new field of study that is using the application of electronic engineering principles to develop concepts for biomedical disciplines. It is a very wide research subject that links engineering and biological sciences with medical science and which has practical importance in the design and development of effective energy-efficient bioelectronics circuit solutions to restore health, extend life as well as to provide solutions in the challenging biomedical device industry. These devices use the application of an electric field to stimulate reactions that restore normal cell functions and activate the biological cells to recover from a disorder or disease. This concept involves the interface between the electronic signal and the biological cells, and how electronic devices and circuitry directly communicate with the electro-active biomolecule system. Albert Szent-Gjorgyi was the first who coined the word "bioelectronics". He showed in his two volumes: introduction to a Sub-Molecular Biology (1960), and Bioelectronics (1968) that all biological cells are electrically charged and have electronic properties comparable to electronic materials [1]. The biological system behaves like a biological microelectronics circuit that acts as a storage medium as in Deoxyribonucleic (DNA) molecules that store and process information by individual molecules. The biological system behaves like biological micro-sensors that possess a range of transducing sensitive systems to detect information about the state of their environment, like the human eye and ear. Furthermore, the biological system behaves like a biological microelectronics circuit that can deliver and control the direction of the electron and the ionic currents along pathways at molecular level by individual electro-active macromolecules. These biological system features can be considered as electronic systems due to their electronic characteristics and act as biological hardware and software that organize and process information [1, 2]. This is inspiring new electronic engineering design for investigating the electro-active biological cell and developing smart electro-medical devices [3]. Since designing a suitable device for electro-medical treatment depends on the condition of the disorder or disease, understanding the biological system features and the disease conditions, from an electronic engineer's point of view, is therefore, essential and potentially beneficial to assist the designer in developing the required electro-medical treatment devices, using the application of an electric field for medical treatment. The application of an electric field for electrotherapy is considered one of the oldest medical treatments since Ancient Greece and the most important documented medical therapies recognized by scientists [4, 5]. It is potentially useful as drug-free relief and overcomes the deficiencies of several conventional medical treatments. It has potential for treating a variety of chronic diseases that have significant social and economic effects. It may assist when therapeutic drugs become useless and cannot be replaced, as in untreatable diseases like cancers and Human immunodeficiency virus that develop drug resistance.

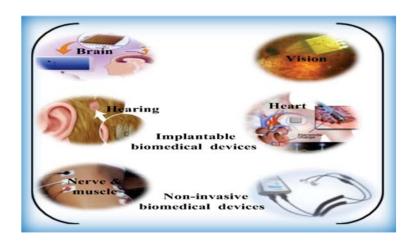

Currently, many biomedical engineering, and medical researchers around the world are using electronic characteristics of biological materials to develop devices that employ electrical stimulation as an effective medical therapy. In modern clinical treatments there are several electro-medical devices that utilize the electrically conductive body medium with the application of electrical fields to improve patients' lives, using either old or new technology for devices that are implanted within the body, and also for non-invasive devices. To our knowledge, both types of devices are important in design considerations for electro-medical treatment. Various electronic devices that are implantable inside the body are developed and have sufficiently enhanced the methods of applying electrical stimulation with no risk. An example is Deep Brain Stimulation (DBS), which delivers electrical current signal to stimulate certain region in the brain, [6]. A microelectronic circuit or a brain implant that is fixed inside the skull under the skin, to make direct contact with the brain surface, transmitting electrical signals that reactivate a paralyzed member in patients with Parkinson' disease, can improve their quality of life [7]. The sub-retinal implantable prosthesis and implantable electrical stimulator for a cochlear prosthesis, which are based on human eye and ear function respectively, use the application of electrical fields, as in the artificial retina implant inside the eye, which produces and sends electrical impulses to the brain to enhance the vision ability [8], and in an optical device

fixed inside the eye as a retina implant to electrically stimulate the cells of the eye which is successfully bringing vision to blind people who have genetic retinal degeneration [9]. Programmable multichannel stimulators based on electrical stimulation of the auditory nerve in the cochlear region are used for cochlear implant prosthesis in deaf patients to recover hearing sensation [10]. Today, more than 130,000 deaf people in the world are using a cochlear implant which allows them to hear normally [3]. Design techniques to provide electrical signals are also used in the cardiac pacemaker system for cardiac activity to improve a patient's heart's rhythms. It has become a remarkably important treatment technique for a slow heart rate [11, 12]. The design of implantable biomedical devices that use the application of electrical stimulation is not limited to the brain, eye, ear, and heart areas. Implantable electrical stimulation devices have been also used for intravesical electrical stimulation (IVES) in diagnosis and treatment of lower urinary tract dysfunction, to enhance bladder sensation and to improve bladder contractility in patients with impaired bladder emptying [13]. Today, implantable electrical stimulation devices are used for vestibular implants to treat balance disorders, brain implants to treat speech disorders, and implants for treating urinary incontinence [3]. Moreover, in a new area of implants, electrical stimulation devices are being developed for the treatment of immune inflammatory disorders of the vagus nerve [14].

The concept of various non-invasive biomedical devices, that only contact the body's cells by using an external electrode, can also be developed for electrical stimulation treatment. These devices use an electrode and the conductivity of the patient's skin cells to communicate, such as sensors for monitoring body's activities, and as in a device that delivers a direct electrical signal onto a patient to stimulate reactions that can heal various pains or disorders and for disease treatment. This can be achieved by treating local inflammation and stimulating muscles, increasing blood flow, and activating natural hormones in the body. An example is a non-invasive transcranial current stimulation, a brain stimulation modality that uses the application of electric fields with a weak electric current, using a pair of electrodes. It is a promising application in modulating brain activity for treatment of brain disorders [15]. Non-invasive transcutaneous electrical nerve stimulation (TENS) utilizes surface electrodes over the posterior tibial nerve which was used for treatment of an overactive bladder (OAB) symptoms [16]. Recently, electrical stimulation to induce the electroporation

effect, has been used for breast cancer therapies when conventional treatments become useless or costly, with serious side effects, and for chemo-resistive patients. This technique specifically controls electric fields of short duration and high intensities, to open up transient pores (aqueous pathways) through semi-permeable membranes and tissues, allowing targeted delivery of therapeutic materials including drugs, antibodies, and genes [17]. Nanosecond pulsed electric field (nsPEF) technology is also used to treat skin cancer in humans. The effects of nsPEF therapy are highly localized to only the cells located between suction electrodes, while tissues outside the edge of the suction electrode show no effects from the therapy [18]. These types of biomedical devices based on electrical stimulation therapy, were approved by America's Food and Drug Administration (FDA) as a standard method for medical treatments, which exist in the market.

The requirement for both types of device is to develop an appropriate biomedical electrical circuit solution for each particular electro-medical treatment device. In both types of smart devices however, it is necessary to generate and deliver an appropriate electrical signal with specific waveform and frequency, to be applied internally or externally to a particular area of the body. Waveform generators (WFG) and electrodes circuitry can communicate with the electro-active biomolecule, highly stimulating certain events arising in a complex biological system. The design of WFG, as well as electrodes, therefore, has become important in a wide range of biomedical signal processing systems. These devices must be portable, miniaturized, adaptable, safe, secure, reliable, operate with low power battery and low cost. Examples of the development of implantable and non-invasive biomedical devices that utilize waveform generators as discussed in this section are summarized in Figure 1.1. Such devices should be accurate, and take into account the interference between biological materials and the device elements. This can be assured by monitoring the biological activities and the responses, with application of an electrical field. These devices must operate at low voltage and be safe to use without exceeding the health safety standards of the International Commission on Non Ionizing Radiation Protection (ICNIRP) and the U.S. Federal Communication Commission (FCC) standards state that human exposure must be restricted to lower levels of electric field [19].

Figure 1.1. Schematic diagram representing the development of a variety of implantable and non-invasive biomedical devices in the real world. These devices use the application of an electric field with an appropriate electrical signal and specific frequency to be applied internally or externally to a particular area of the body, to treat a variety of disorders or disease conditions, and to improve patients' lives [3][7][9].

The applications of biomedical integrated circuits (IC) design are promoted and increase every day. CMOS (Complementary Metal-Oxide Semiconductor) technology is used widely today to design small-size and low-power consumption biomedical devices. This research project addresses the design and development of a smart non-invasive battery operating biomedical device, using a new 130 nanometer (nm)-CMOS technology for bio-electrical treatment which can generate, control and deliver a periodical low frequency bipolar square waveform signal and low voltage electrical field through the low-resistance skin surface to a patient's blood, to stimulate a reaction in order to hopefully treat body fluid related pathogens, particularly HIV-1. Given the massive burden of the illnesses on patients, it is necessary to develop novel alternative treatments that exceed the current pharmaceutical therapeutic approaches in terms of efficiency and safety. It can be used when conventional treatments become useless and costly, with serious side effects, and for drug resistive patients. Essentially, advances in bio-electro-chemistry science in understanding cellular function and response, as well as the heterogeneous structure of the proteins (which comprise various conductivities and permittivity, that determining the interaction with the electrical field), inspires the conceptual design of treatments based on a systematic consideration of the fundamentals of disease development. In particular, an interaction of the HIV-1 and

host cell proteins, that is dominated by electrostatic interactions, considered the main driving forces for the progress of the disease state, represents a desirable objective for such an approach. Therefore, this research project will introduce the underlying mechanism of the disease and outline a path that will combine bio-electrochemistry science at the molecular level, engineering principles and medical science to advance functional design in vitro as a promising foundation and value for the establishment of HIV-1 treatment in vivo.

#### 1.2 Relevance

Today, health care issues demand concern all around the world. It is an area that involves private and public sectors with significant social and economic impacts. Good health is essential for carrying out the basic daily life tasks through to the development of nations. The development of societies is evaluated according to the health of their people, because health is a balance between people and their environment. People with illness or chronic pain may struggle to participate and communicate with others in everyday life. This may occur in both chronic illness and unexpected disease which can be an enormous psychological burden and can cause serious handicaps, especially if the disease causes feebleness or death in human and in economically important animals. The impact of such disease is measured by financial cost, mortality and morbidity. Pathogenic disease is considered the greatest cause of death, and kills millions of people worldwide every year, more than all other diseases [20-23]. Most pathogenic diseases are infectious and caused by a micro-organism such as fungi, bacteria, and viruses, which affects the normal physiological functions by causing dysfunction or tissue damage. However, there are different types of pathogenic disease around the world which need significant consideration.

The major three pathogenic diseases that cause about half of all deaths in the world are tuberculosis (TB), malaria and AIDS. These diseases pose a continuous threat globally, because of increased immigration and travel. HIV-1 and TB are also multidrug resistant and because of co-infection of HIV-1 with TB and it is one of the risk factors for development of cancer in humans that increases death rates annually for the next 10 years [20]. In 2010, it was estimated that 34 million people were living with HIV-1, 3 million people were diagnosed with HIV-1 infection and 2 million people had died from

AIDS [21]. Thus it can be concluded that HIV-1 disease can be a significant economic burden including healthcare-associated infections (HAI) and costs involving hospital, nursing, laboratory and diagnostics, investigations, medical treatment, outbreaks of disease and infection prevention, time and loss of production. In United States, the cost burden for HAI is between about 25.0 and 31.5 billion dollars per year. In English hospitals, it was estimated at 1.6 billion dollars which is 1% of the total national hospital budget. The global goal is to prevent and treat disease, to reduce the disease burden. Many health organizations such as the World Health Organization (WHO) and Centre for Disease Control and Prevention (CDC) are organizing and monitoring many treatment programs and have developed a strategy for the 21st Century that improves the people's health, to reduce the chronic disease death rates annually for the next 10 years, by 2%. The four major goals of the CDC are: a) surveillance and response, b) applied research, c) infrastructure and training, and d) prevention and control. Achieving these goals will assist in treating pathogenic disease, particularly HIV-1 now, and preventing it tomorrow [22, 23].

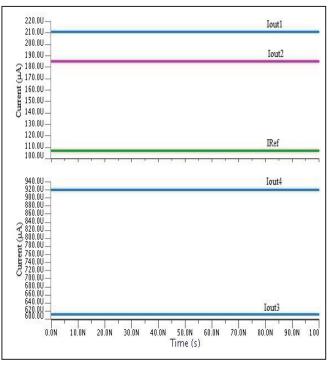

#### 1.2.1 Virus Replication